#### THE BELL TELEPHONE LABORATORIES SERIES

Speech and Hearing - Harvey Fletcher

Probability and Its Engineering Uses - Thornton C. Fry

Elementary Differential Equations (Second Edition) - Thornton C. Fry

Transmission Circuits for Telephonic Communication - K. S. Johnson

Transmission Networks and Wave Filters - T. E. Shea

Economic Control of Quality of Manufactured Product - W. A. Shewhart

Electromechanical Transducers and Wave Filters (Second Edition) - Warren P. Mason

Electromagnetic Waves - S. A. Schelkunoff

Network Analysis and Feedback Amplifier Design - Hendrik W. Bode

Servomechanisms - LeRoy A. MacColl

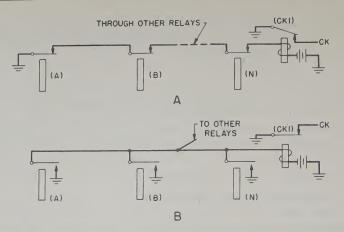

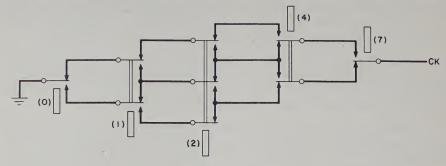

Quartz Crystals for Electrical Circuits - R. A. Heising

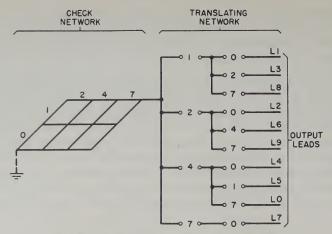

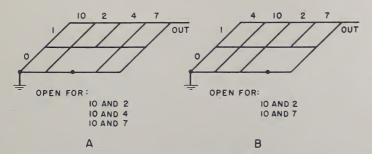

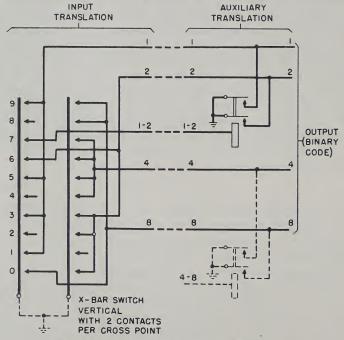

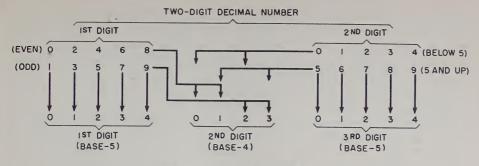

Capacitors: Their Use in Electronic Circuits - M. Brotherton

Fourier Integrals for Practical Applications - George A. Campbell and Ronald M. Foster

Visible Speech - Ralph K. Potter, George A. Kopp, and Harriet C. Green

Applied Mathematics for Engineers and Scientists - S. A. Schelkunoff

Earth Conduction Effects in Transmission Systems - Erling D. Sunde

Radar Systems and Components - Members of the Staff of the Laboratories Introduction by M. J. Kelly

Theory and Design of Electron Beams - J. R. Pierce

Piezoelectric Crystals and Their Application to Ultrasonics - Warren P. Mason

Microwave Electronics - John C. Slater

Principles and Applications of Waveguide Transmission - George C. Southworth

Traveling-Wave Tubes - J. R. Pierce

Electrons and Holes in Semiconductors - William Shockley

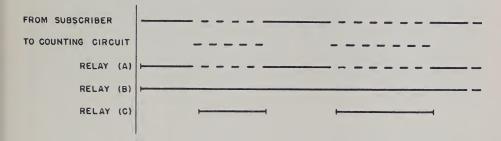

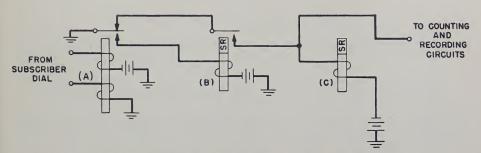

Ferromagnetism - Richard M. Bozorth

The Design of Switching Circuits - William Keister, Alistair E. Ritchie, and Seth H. Washburn

# THE DESIGN OF SWITCHING CIRCUITS

BY

# WILLIAM KEISTER ALISTAIR E. RITCHIE SETH H. WASHBURN

MEMBERS OF THE TECHNICAL STAFF BELL TELEPHONE LABORATORIES

## D. VAN NOSTRAND COMPANY, INC.

TORONTO NEW YORK LONDON

#### NEW YORK

D. Van Nostrand Company, Inc., 250 Fourth Avenue, New York 3

#### TORONTO

D. Van Nostrand Company (Canada), Ltd., 228 Bloor Street, Toronto

#### LONDON

Macmillan & Company, Ltd., St. Martin's Street, London, W.C.2

Copyright, 1951, by D. VAN NOSTRAND COMPANY, INC.

Published simultaneously in Canada by D. Van Nostrand Company (Canada), Ltd.

#### All Rights Reserved

This book, or any parts thereof, may not be reproduced in any form without written permission from the authors and the publishers.

То

N., J., and J.

#### FOREWORD

The present is an excellent time for this book to appear. In the past, general interest in the switching art and knowledge of its unique techniques were limited to a few quarters where complex control mechanisms such as telephone switching systems were developed and used. Now, however, the situation is changing rapidly and radically. College professors, research engineers, scientists, and mathematicians are now aware of and keenly interested in the subject. This change was brought about, or at least greatly accelerated, by the appearance of automatic digital computing systems. Fundamentally, such systems employ essentially, the same techniques as those useful in telephone switching. However, their ability to perform complicated mathematical calculations furnished a brilliant and readily understandable demonstration of the fact that switching circuits can be designed to accomplish, mechanically, at least certain sorts of operations which are normally associated with human mental effort. For example, they can follow trains of orders, they can make use of tables, they can make deductions following formal logical rules. Of course, in other respects such mechanisms may be sadly lacking in comparison with human intelligences. The abilities they do have, however, seem great enough to promise the elimination of much of the mental drudgery required by our modern world. It is this glimpse of a coming age of "mechanized intelligence" that recently caught the imagination of professional people and caused the upsurge of interest in switching. If this textbook succeeds in nourishing that interest, and if it helps its readers to work toward the ultimate realization of such a significant goal, the effort that went into its preparation will indeed have served a very worthy purpose.

The book is a natural product of the Bell Telephone Laboratories, since the design of switching circuits to establish telephone connections is a basic and vital activity of this organization.

When we make a telephone call, we spin our dial a few times, and — in a matter of seconds — the particular phone that we want among millions of others is ringing. This happens with such regularity and such reliability that we have come to take it for granted. Most of us never try, or for that matter are not able, to visualize the series of intricate events that take place automatically in a modern dial telephone office before that called phone is rung.

In simple terms, what happens is that at the instant we lift our handset, a group of switching circuits springs obediently to our service. These switching circuits identify our line as the one in need of attention, connect themselves to it, give us the signal to proceed, count our dial pulses, memorize the series of digits, determine our call's destination, locate and test the available paths, select the most preferred combination, join the links end-to-end, and finally, when the connection is all set, ring the wanted phone.

All this is accomplished for us in seconds by the switching circuits of the dial central office. Just for perspective, it is also worth noting that while one group of switching circuits works on our call, additional groups, in perfect teamwork, are taking prompt care of the random requests of thousands of other customers.

Obviously, then, switching circuits used in dial central offices are swift and versatile mechanical servants; and even if they did no more than establish connections, when we are once aware of their existence, we are likely to be intrigued by them. However, they go further in their performance. To facilitate proper charging for their services, these switching circuits also record who calls whom, and when, and how long each conversation lasts. Such competence on their part certainly increases our respect for them.

Even this is not all. As a little extra service during their daily work, these central office circuits make a second attempt at setting up a connection in case their first attempt fails; or they locate alternative routes to a destination if the preferred one is not available, or furnish maintenance men with precise information regarding troubles, and so on.

This roll-call of events in a dial central office conveys, perhaps, an adequate sense of the type of actions that switching circuits can perform. It also reveals how far the ingenuity, imagination, and precise logic of design engineers have advanced the art in a particular field of application. Such a revelation may induce readers of this textbook to go beyond its Foreward. Those who do, will find a wealth of switching fundamentals, succinctly rationalized and presented by the authors.

Since the material for this book was prepared as part of a post-war training program for young engineers at the Bell Telephone Laboratories, it is appropriate to close this Foreword with a simple tribute to the Laboratories' management, particularly Mr. A. B. Clark, Vice President, for initiating and firmly supporting such a training program on the basis of its long-term merits, when there was intense

Foreword

need for manpower in more immediately profitable switching development projects. In years to come, the training program will bring a harvest in the form of technical contributions by the young engineers whose minds have been alerted to the challenges of the switching art. For the present, it is hoped that this book, a direct outcome of the training program, will be a tangible source of satisfaction to those whose official support it represents.

JOHN MESZAR

July 1951

#### PREFACE

This book is not a text on telephone systems. It is concerned, rather, with the basic techniques of switching circuit design: techniques which are applicable to digital computers and other complex control systems as well as telephone switching systems. The writing of this text was started soon after the end of World War II as a series of lecture notes for use in training new engineers in the Switching Systems Development Department of the Bell Telephone Laboratories. During the succeeding years the notes were revised and the methods of instruction were improved. In 1950, with general interest in the subject of switching increasing, arrangements were made with the Massachusetts Institute of Technology to give to graduate students a onesemester course in switching circuit design. The text for this course was based on the material used for training within the Laboratories. The present volume is a final edition of the text used in the M. I. T. course, revised to take advantage of the academic experience gained there.

The objective of this book is to present the fundamental principles underlying the design of switching circuits rather than to describe the operation of specific circuits, except as examples. The material is planned to be complete within itself, no previous knowledge of switching being assumed. For this reason explanations are often given in considerable detail. The book is suitable for individual study as well as for a one-semester or two-semester course of formal instruction. The only prerequisites for its use are a logical mind and a knowledge of elementary electrical circuit theory.

The subjects of the chapters range from elementary concepts to the design of circuits containing a relatively large number of switching devices. Chapter 1 serves as an introduction to the subject. Chapter 2 discusses the physical and electrical characteristics of the various devices used for switching. Chapters 3 through 10 give the fundamentals of switching circuit design, including the logical concepts involved and the form of Boolean algebra which has been given the name "Switching Algebra". Chapters 11 through 21 discuss "unifunctional circuits", which are aggregates of switching devices performing single specific switching actions. These are the building blocks of large switching systems. The last three chapters contain a brief treatment of the methods of synthesizing such basic functional circuits into practical

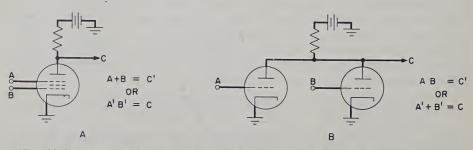

working systems. Principles and techniques are illustrated primarily by relay switching circuits. However, electronic techniques employing tubes, rectifiers, and transistors are discussed and many examples are given. Of particular interest in this regard are Chapter 10, which discusses electronic circuit fundamentals, and Section 21.7 of Chapter 21, which illustrates the application of switching algebra to the design of electronic switching circuits.

On the basis of teaching experience, it is felt that design practice is the best way to gain facility in the application of principles. Following most chapters is a set of suitable problems which have been tested by actual classroom use. Since almost all switching problems have a number of satisfactory answers, the solutions are sometimes difficult to judge. As a guide, the approximate quantity of apparatus required for a good solution is given in many of the problems. This is not always the minimum possible apparatus but represents a reasonable point to which a circuit may be reduced. In learning the subject, it is also helpful for the student actually to build circuits from original designs. Many of the problems are suitable for this activity. Particular attention is called to the special problem given at the end of Chapter 11.

The basic ideas presented in this text have, for the most part, been distilled from the accumulated work of practicing circuit design engineers. A number of people have contributed directly to the work leading up to the publication of this book. Mr. A. E. Joel was associated with the authors in the early stages of the teaching program and contributed valuable ideas, particularly in the organization of functional circuits. Messrs. G. R. Frost and W. S. Hayward prepared the first drafts of several chapters. Messrs. R. W. Roberts and H. N. Seckler assisted in the details of producing the final text. The book was designed by Mr. K. M. Collins, who not only handled all problems of publication and printing, but made available to the authors a wealth of information and experience in the fine art of preparing a bookfor public presentation. Finally, the authors wish to express their appreciation for the friendly advice, encouragement, and discerning criticism of Mr. John Meszar in all of the activities leading up to the production of this book.

> WILLIAM KEISTER ALISTAIR E. RITCHIE SETH H. WASHBURN

## LIST OF CHAPTERS AND MAJOR SECTIONS

# CHAPTER 1 PAGE 1 Fundamental Control Concepts

|                                                             | CHAPTER 2 PAGE 9                                                                                                                                                                                                                                                                                     |                                                                                         |

|-------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

|                                                             | Switching Apparatus                                                                                                                                                                                                                                                                                  |                                                                                         |

| 2.1<br>2.2<br>2.3<br>2.4<br>2.5                             | General-Purpose Relays                                                                                                                                                                                                                                                                               | Page 10<br>Page 21<br>Page 23<br>Page 24<br>Page 26                                     |

|                                                             | CHAPTER 3 PAGE 27                                                                                                                                                                                                                                                                                    |                                                                                         |

|                                                             | Basic Relay Control Paths                                                                                                                                                                                                                                                                            |                                                                                         |

| 3.1<br>3.2<br>3.3                                           | Basic Control Methods for Relays with Single Windings.  Summary of the Four Basic Control Methods.  Relays with Special Characteristics.  Problems.                                                                                                                                                  | Page 27<br>Page 30<br>Page 31<br>Page 34                                                |

|                                                             | CHAPTER 4 PAGE 36                                                                                                                                                                                                                                                                                    |                                                                                         |

|                                                             | Relay Contact Network Configurations                                                                                                                                                                                                                                                                 |                                                                                         |

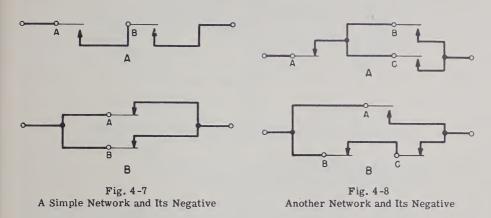

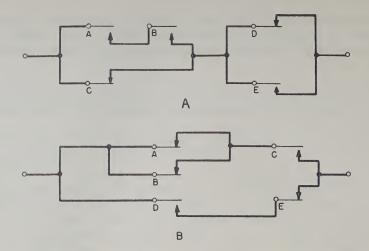

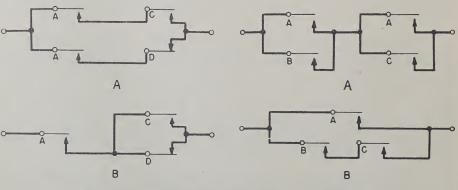

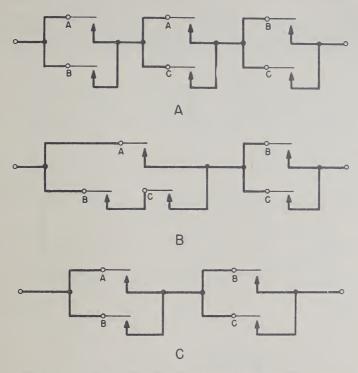

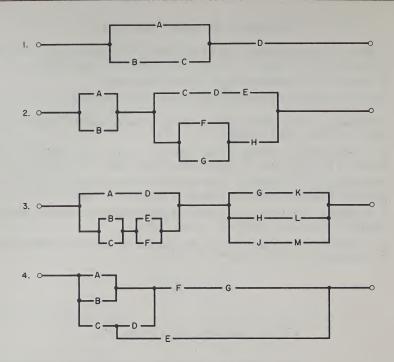

| 4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6<br>4.7<br>4.8<br>4.9 | Logic of Contact Networks.  "And-Or" and Series-Parallel Relationships.  The Negative Relation.  Basic Simplifications in Two-Terminal Network Design  Bridge-Type Networks  Multi-Terminal Networks  Transfer Contacts in Networks  Transfer-Tree Circuits.  Transfer Chains.  Reiterative Networks | Page 36 Page 37 Page 38 Page 40 Page 43 Page 45 Page 46 Page 50 Page 54 Page 55 Page 64 |

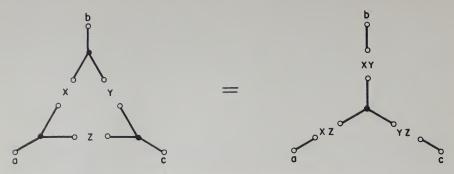

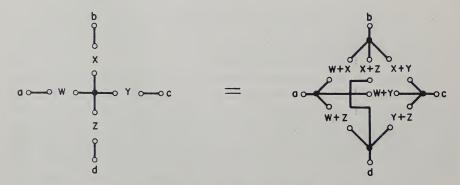

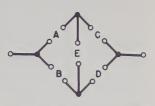

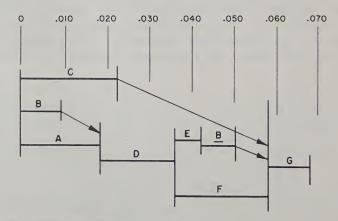

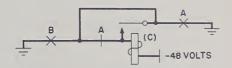

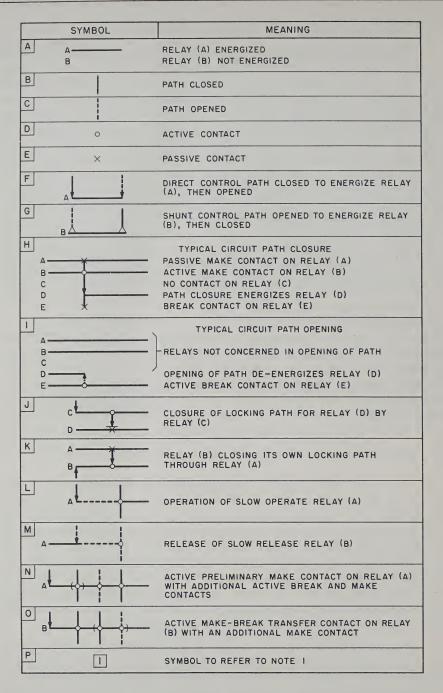

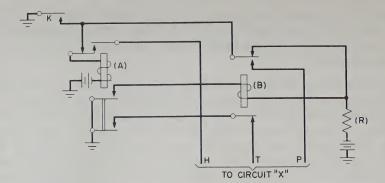

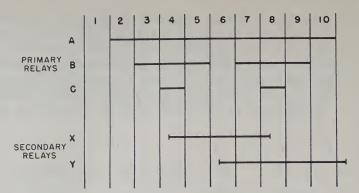

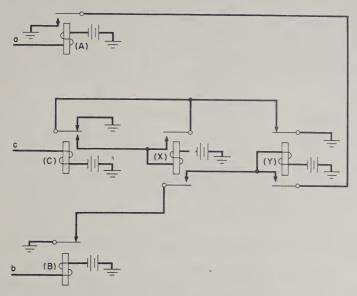

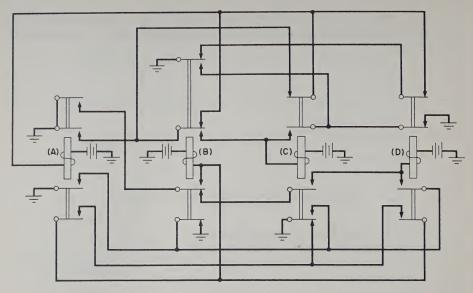

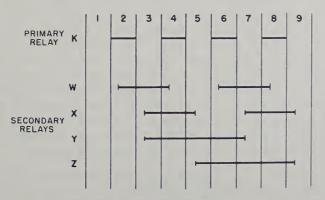

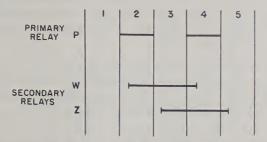

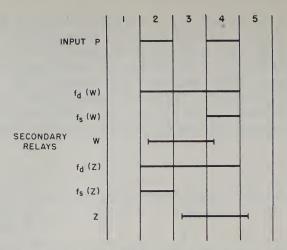

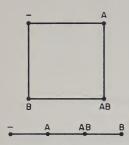

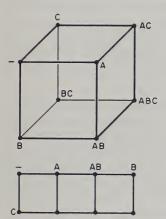

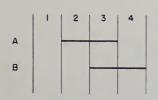

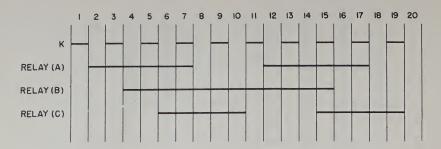

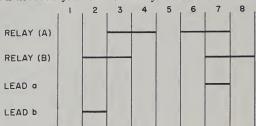

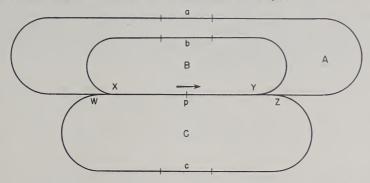

#### CHAPTER 5 PAGE 68 Switching Algebra, and Manipulation of Relay Contact Networks Symbolic Notation in Switching Algebra ....... 5.1 Page 69 5.2 Page 70 5.3 Page 71 5.4 General Notes on Network Simplification and Manipulation. . . . . . Page 81 5.5 Page 83 5.6 Page 89 Delta-Y Transformations..... Page 93 5.7 5.8 Resolution and Synthesis of Bridge-Type Networks...... Page 95 5.9 Page 99 5.10 Recapitulation of the Postulates and Theorems ....... Page 101 Page 103 Page 103 CHAPTER 6 **PAGE 108** Design of Combinational Relay Circuits 6.1 Page 108 6.2 Page 109 6.3 Page 110 6.4 Page 110 6.5 Page 111 6.6 Page 112 6.7 Temporary False Output Conditions..... Page 127 Page 128 CHAPTER 7 **PAGE 131** Time Charts, Sequence Diagrams, Simplified Schematics, and Graphic Descriptions of Relay Circuits 7.1 Page 132 7.2 Page 136 7.3 Partial Schematic Drawings or "Shorts"..... Page 137 7.4 Page 137 CHAPTER 8 **PAGE 142** Design of Sequential Relay Circuits 8.1 Control of Secondary Relays..... Page 144 8.2 Page 155 8.3 Page 156 8.4 Developing an Operating Sequence..... Page 156 8.5 Page 159 Illustrative Examples of Sequential Circuit Design . . . . . . . . . . 8.6 Page 165 8.7 Appendix: Development of an Operating Sequence for a Group of Relays Page 172

Page 175

|                                                      | CHAPTER 9 PAGE 179                                                                                                                                                                                                                                                                 |                                                                                              |

|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

|                                                      | Elementary Switch Control Circuits                                                                                                                                                                                                                                                 |                                                                                              |

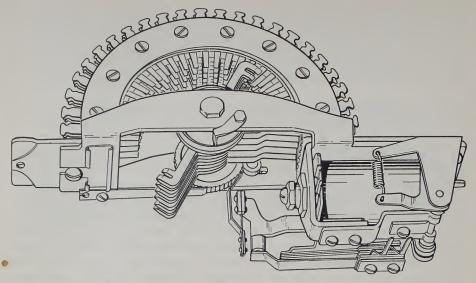

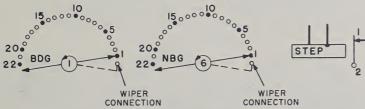

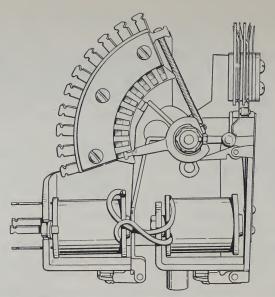

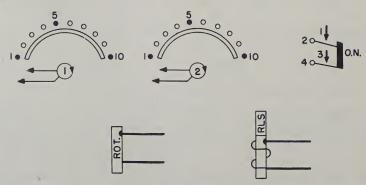

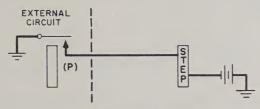

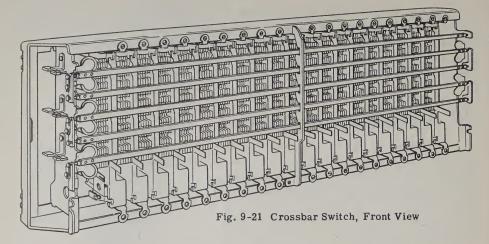

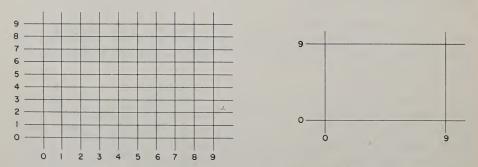

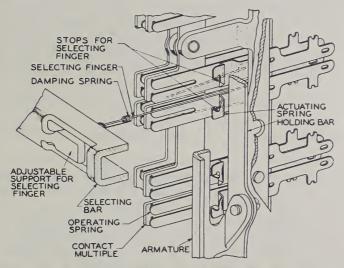

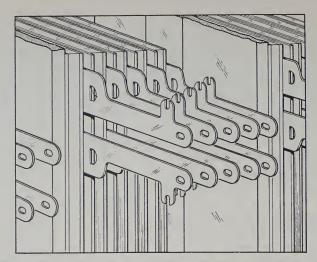

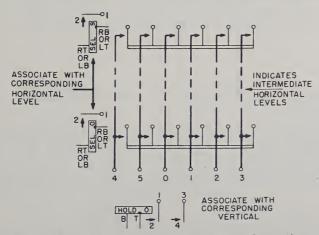

| 9.1<br>9.2<br>9.3<br>9.4<br>9.5<br>9.6<br>9.7<br>9.8 | Rotary Selector Switches: Mechanical Considerations Control of Rotary Selector Switches. Switch Stepping Circuits Switch Running Circuits. Switch Halting Circuits Switch Restoring Circuits Crossbar Switches: Mechanical Considerations. Control of the Crossbar Switch Problems | Page 179 Page 183 Page 183 Page 186 Page 189 Page 193 Page 194 Page 196 Page 199             |

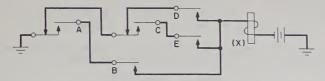

|                                                      | CHAPTER 10 PAGE 202                                                                                                                                                                                                                                                                |                                                                                              |

|                                                      | Elementary Electronic Switching Circuits                                                                                                                                                                                                                                           |                                                                                              |

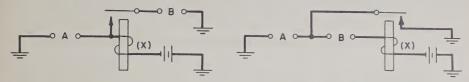

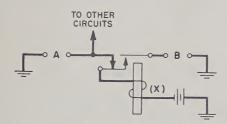

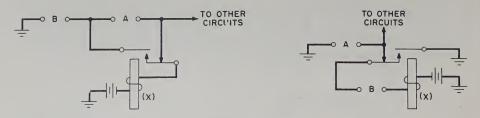

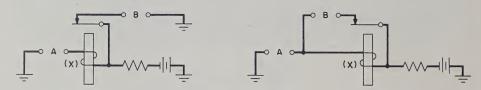

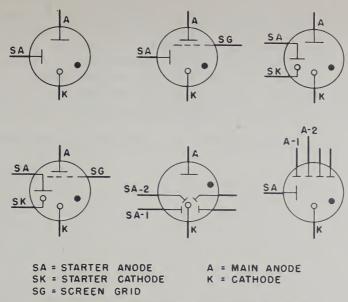

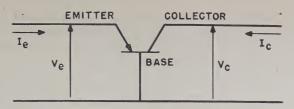

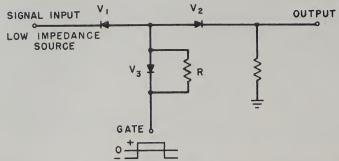

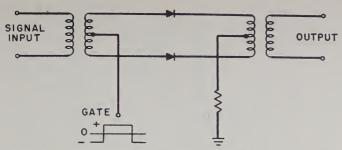

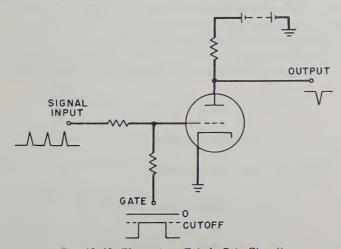

| 10.1<br>10.2<br>10.3                                 | Characteristics of Electron Tubes and Semi-Conductors as Switching Elements Basic Tube and Semi-Conductor Circuits for Switching Applications Electrostatic and Magnetic Effects in Electronic Switching Circuits Problems                                                         | Page 203<br>Page 207<br>Page 232<br>Page 233                                                 |

|                                                      | CHAPTER 11 PAGE 235                                                                                                                                                                                                                                                                |                                                                                              |

|                                                      | Circuits for Counting                                                                                                                                                                                                                                                              |                                                                                              |

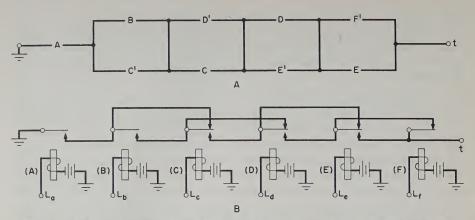

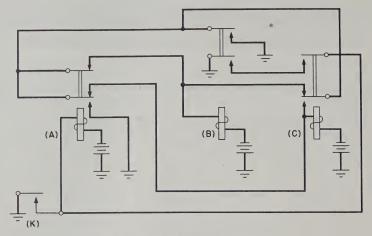

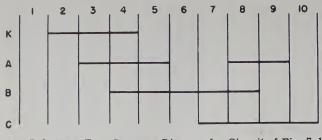

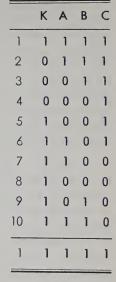

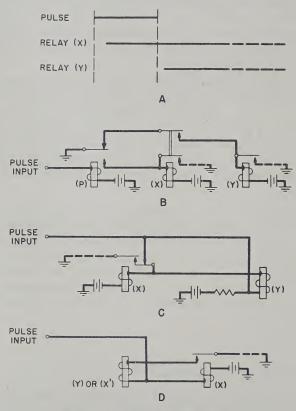

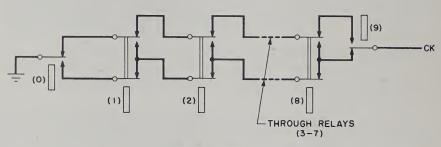

| 11.1<br>11.2<br>11.3<br>11.4<br>11.5                 | Systems of Enumeration Basis of Relay Counting-Circuit Design Single-Pulse Counters. Two-Pulse Counters or Pulse-Frequency Dividers. Counting a Train of Pulses. Sequence Circuits. Problems Special Problem.                                                                      | Page 236<br>Page 239<br>Page 239<br>Page 242<br>Page 247<br>Page 267<br>Page 272<br>Page 273 |

|                                                      |                                                                                                                                                                                                                                                                                    |                                                                                              |

|                                                      | CHAPTER 12 PAGE 275                                                                                                                                                                                                                                                                |                                                                                              |

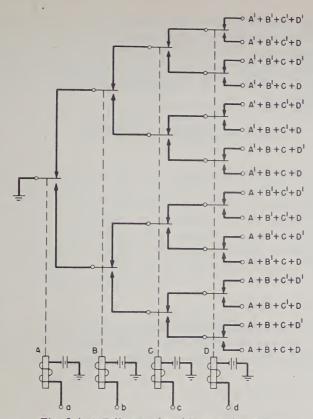

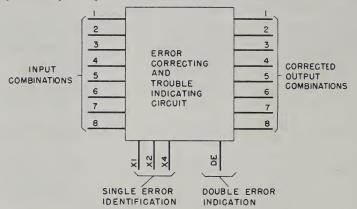

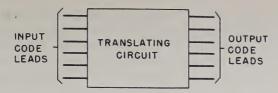

|                                                      | Codes and Translating Circuits                                                                                                                                                                                                                                                     |                                                                                              |

| 12.1<br>12.2<br>12.3<br>12.4<br>12.5<br>12.6         | How Information is Represented Simple Combinational Codes. Self-Checking Codes The Theory of Error-Detecting and Error-Correcting Codes Translating Circuits Design Techniques for Translating Networks.                                                                           | Page 277<br>Page 278<br>Page 280<br>Page 281<br>Page 288<br>Page 289                         |

|                                                      |                                                                                                                                                                                                                                                                                    |                                                                                              |

|                | 42 (20)                                             |                      |

|----------------|-----------------------------------------------------|----------------------|

|                | CHAPTER 12 (CONTINUED)                              |                      |

| 12.7           | Examples Illustrating Design Techniques             | Page 292             |

| 12.8           | Further Examples Based on Standard Codes            | Page 295             |

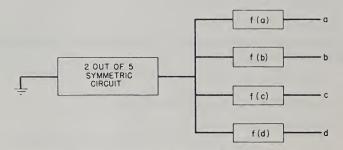

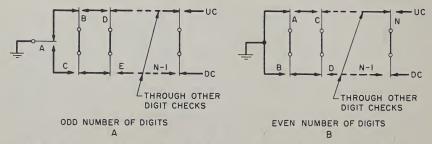

| 12.9           | Symmetric Checking Networks                         | Page 298             |

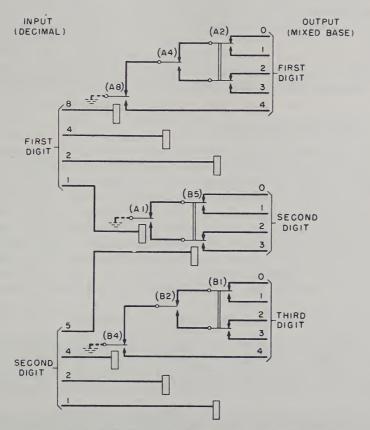

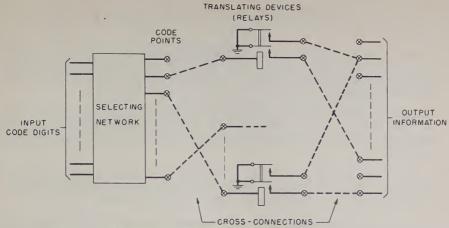

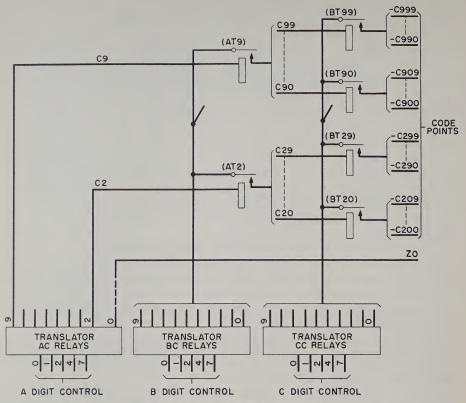

| 12.10<br>12.11 | Intermediate Translation                            | Page 299<br>Page 300 |

| 12.11          | Large Translators                                   | Page 300             |

| 12.12          | Problems                                            | Page 304             |

|                |                                                     |                      |

|                | CHAPTER 13 PAGE 306                                 |                      |

|                | Circuits for Selecting                              |                      |

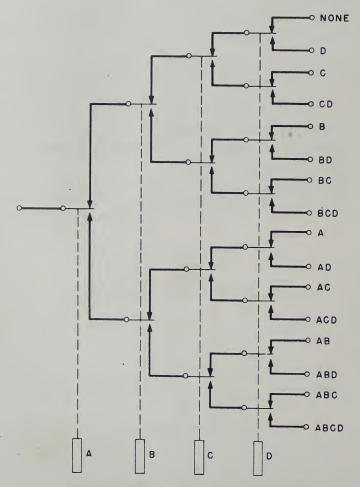

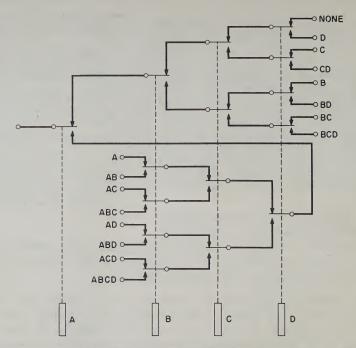

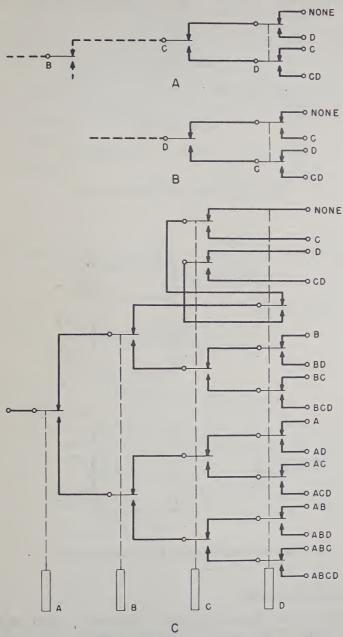

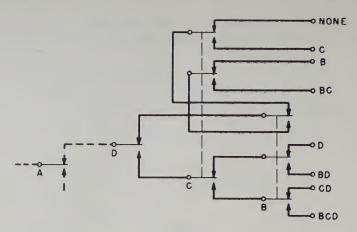

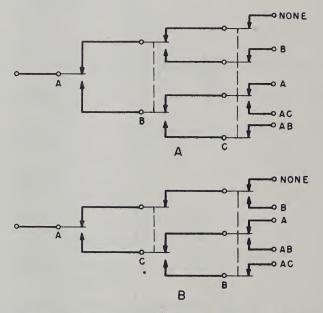

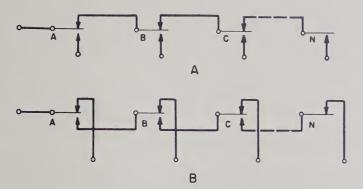

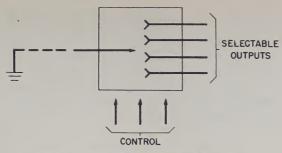

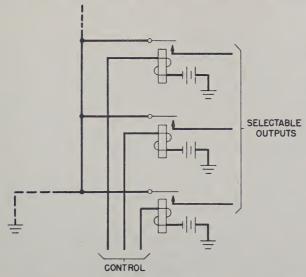

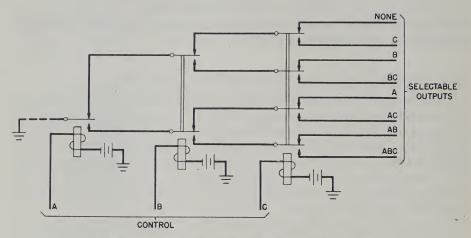

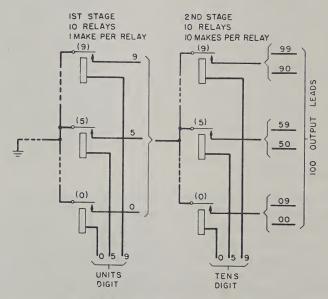

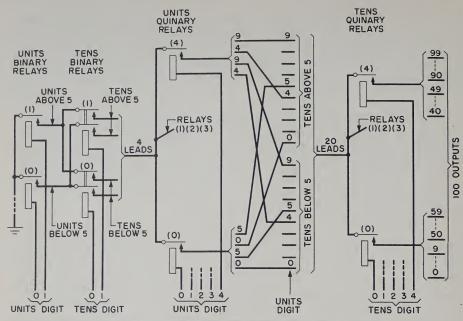

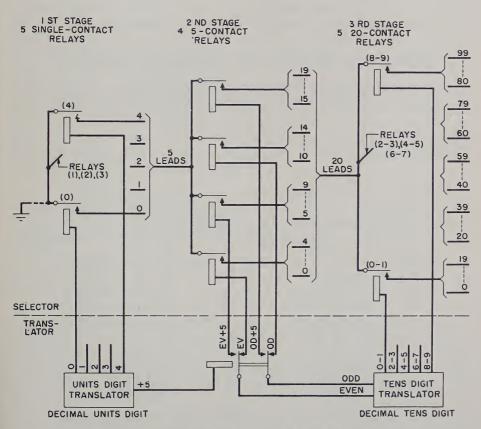

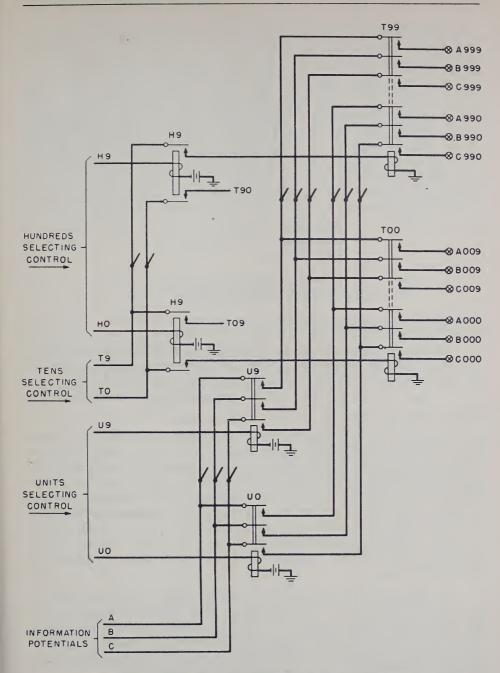

| 13.1           | Elementary Relay Selecting Circuits                 | Page 307             |

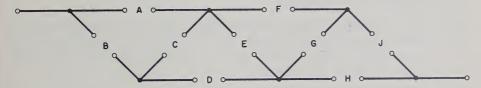

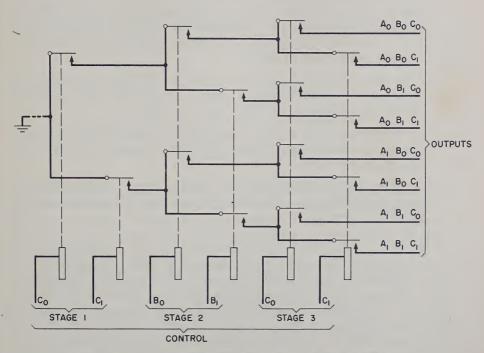

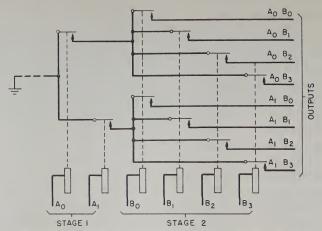

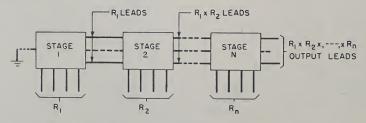

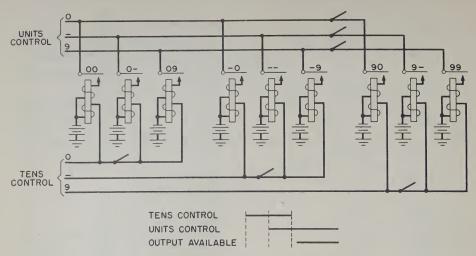

| 13.2           | Multibranch Trees: General                          | Page 309             |

| 13.3           | Theoretical Considerations of Multibranch Trees     | Page 310             |

| 13.4           | Practical Considerations: Size of Relays            | Page 312             |

| 13.5           | Practical Considerations: Control Codes             | Page 314             |

| 13.6           | Modification of Selecting Trees                     | Page 317             |

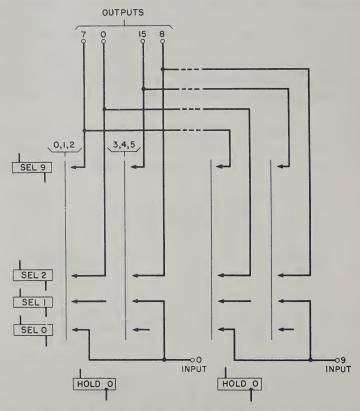

| 13.7           | Use of Selecting Circuits in Large Translators      | Page 318             |

| 13.8           | Selection by Sequential Control                     | Page 322             |

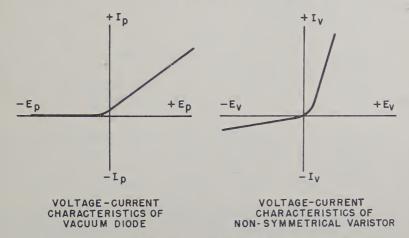

| 13.9           | Selection with Non-Symmetrical Varistors            | Page 323             |

|                | Problems                                            | Page 325             |

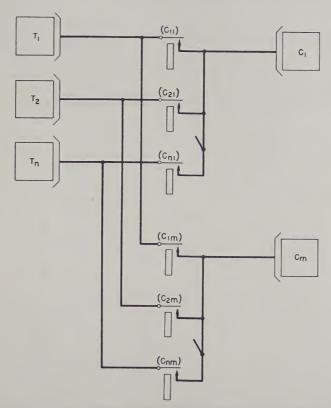

|                | CHAPTER 14 PAGE 327                                 |                      |

|                | Circuits for Connecting                             |                      |

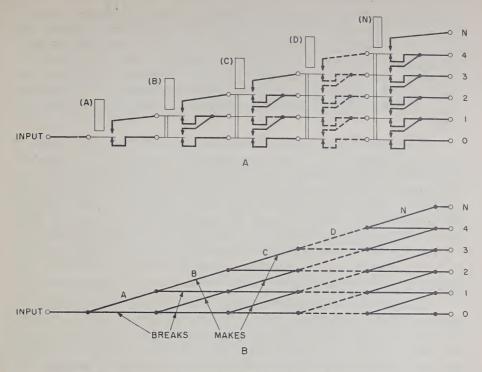

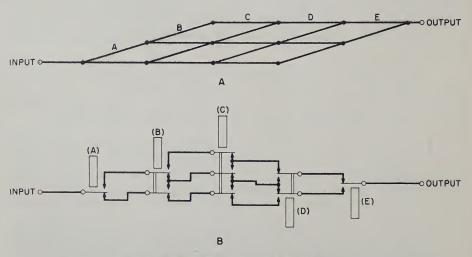

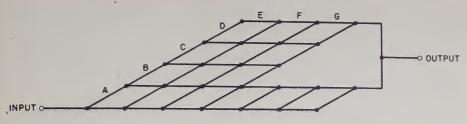

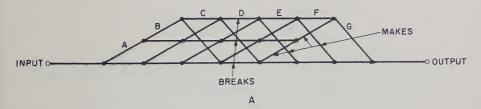

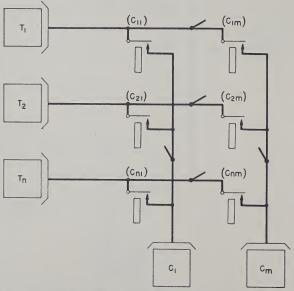

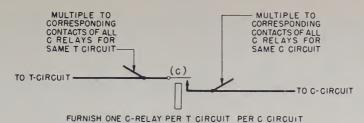

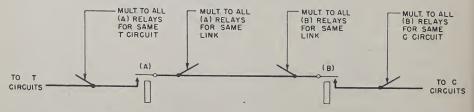

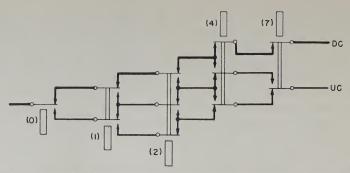

| 14.1           |                                                     | D. 000               |

| 14.1<br>14.2   | The Multiple Many-to-Many Connections by Multiple   | Page 330             |

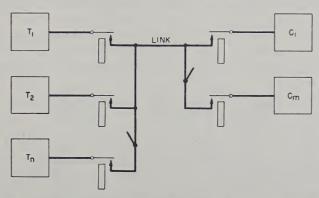

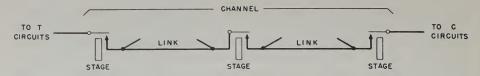

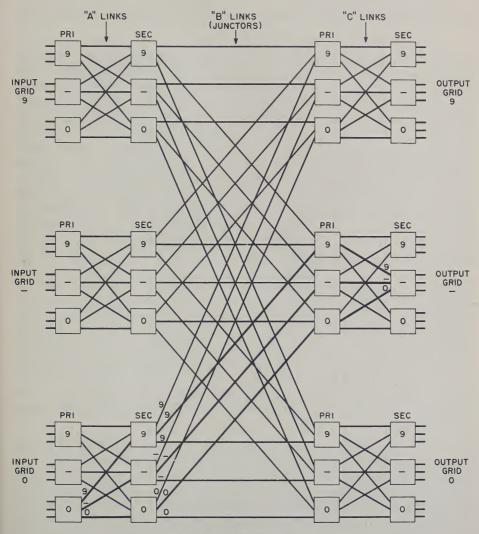

| 14.3           | Links                                               | Page 331<br>Page 333 |

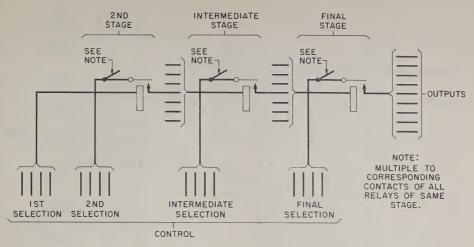

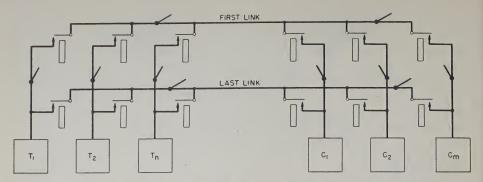

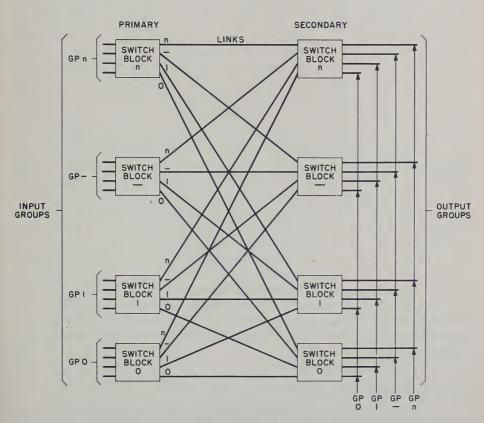

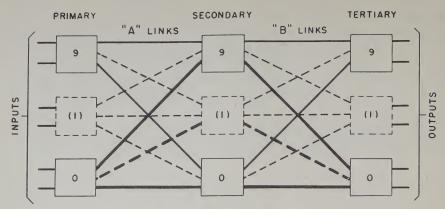

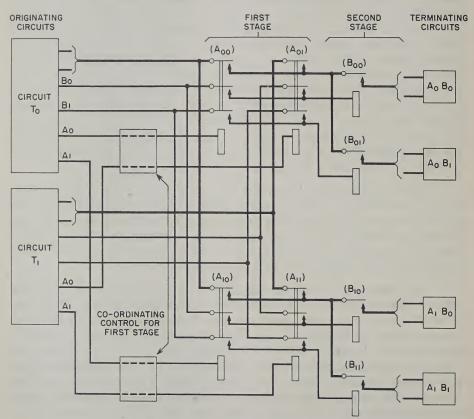

| 14.4           | Multistage Connecting                               | Page 335             |

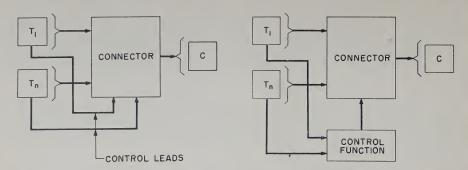

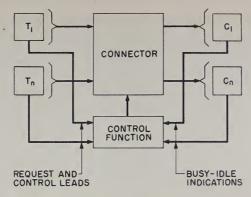

| 14.5           | Control of Connecting Circuits                      | Page 338             |

| 14.6           | Combined Selecting and Connecting                   | Page 342             |

|                | Problems                                            | Page 343             |

|                |                                                     |                      |

|                |                                                     |                      |

|                | CHAPTER 15 PAGE 344                                 |                      |

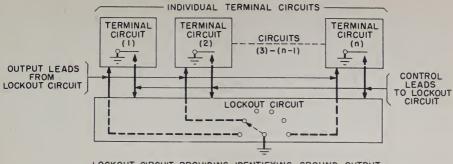

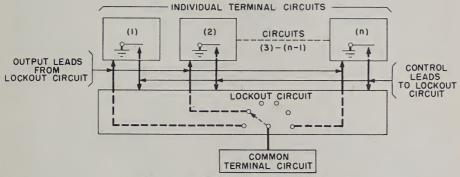

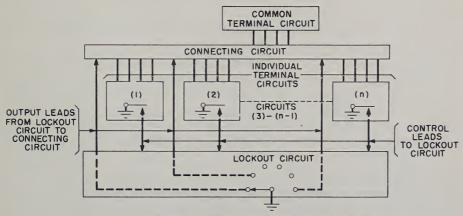

|                | Circuits for Lockout                                |                      |

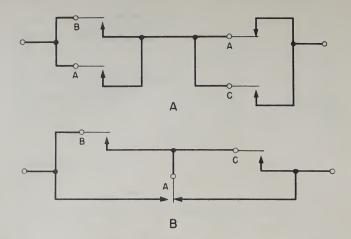

| 15.1           | The Double-Transfer Lockout Circuit                 | Page 347             |

| 15.2           | End-Relay Lockout Circuits                          | Page 351             |

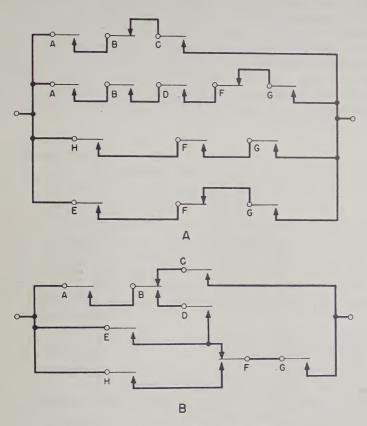

| 15.3           | Gate-Type Lockout Circuits                          | Page 353             |

| 15.4           | Varying the Order of Preference in Lockout Circuits | Page 355             |

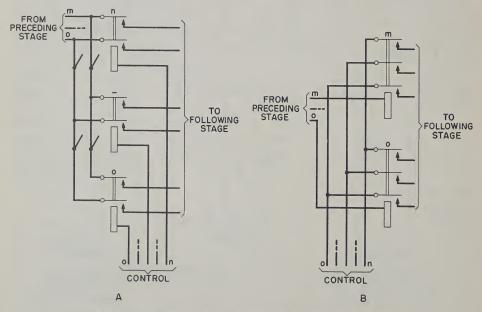

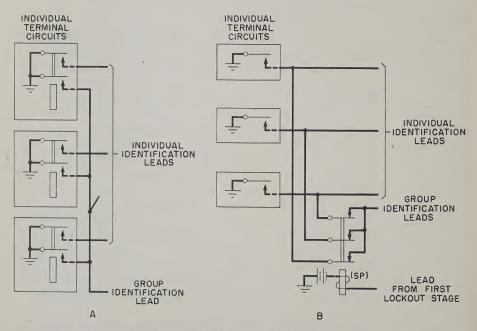

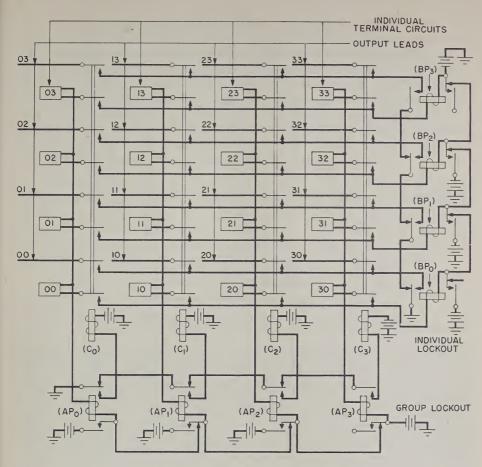

| 15.5           | Multistage Lockout Circuits                         | Page 357             |

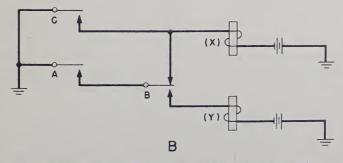

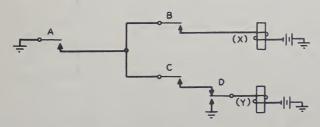

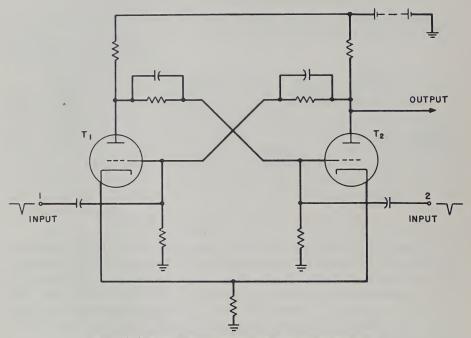

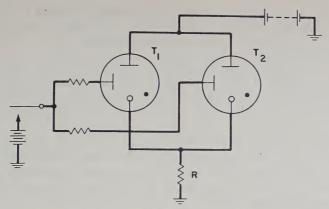

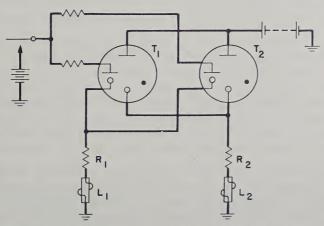

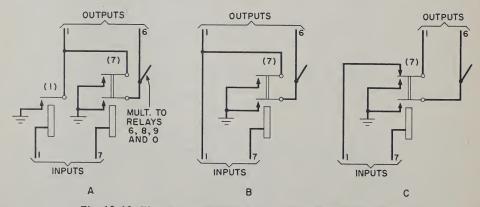

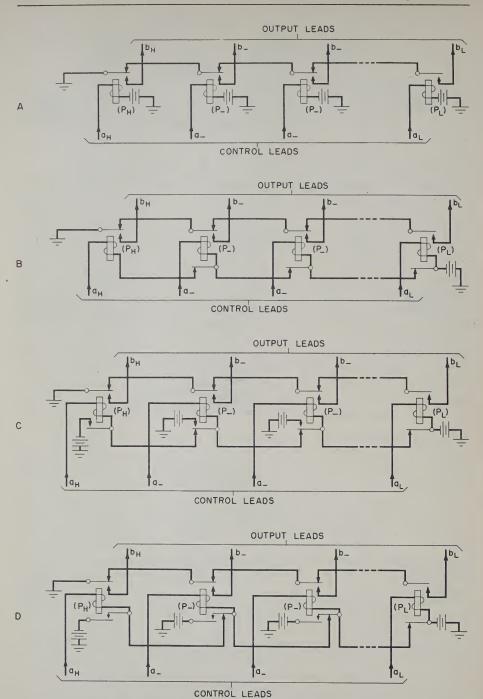

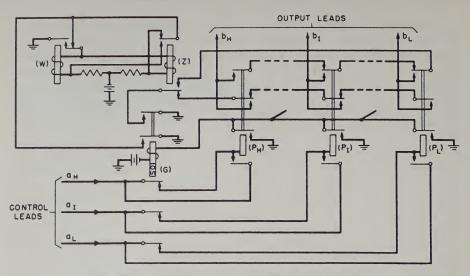

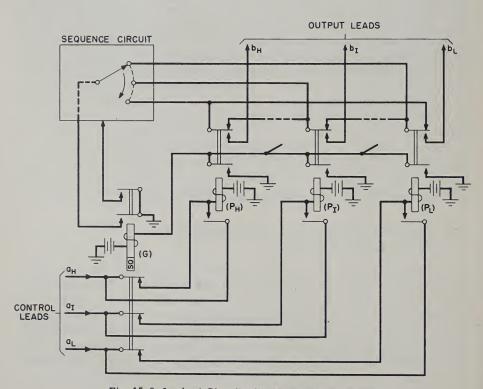

| 15.6           | Electronic Lockout Circuits                         | Page 358             |

|                | Problems                                            | Page 363             |

|                |                                                     |                      |

ing day 1911 sa ang mang ang mga ang m

|                                              | CHAPTER 16 PAGE 365                                                                                                                                          |                                                                      |

|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

|                                              | Circuits for Finding and Hunting                                                                                                                             |                                                                      |

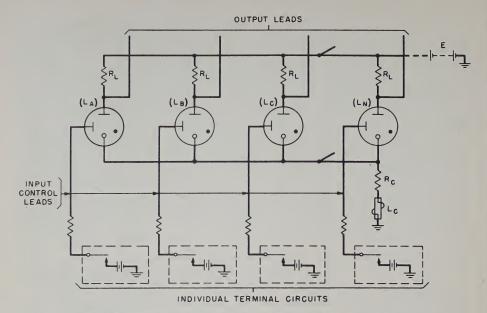

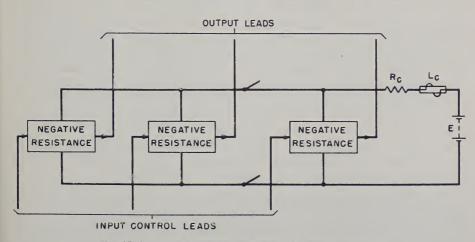

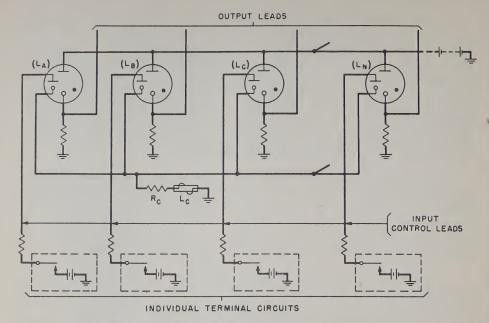

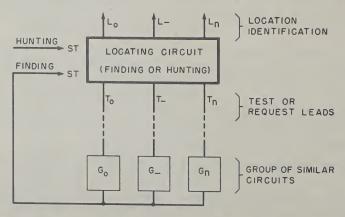

| 16.1<br>16.2<br>16.3<br>16.4                 | Basic Requirements of Finding and Hunting Circuits. Finding Circuits. Hunting Circuits. Electronic Hunting Circuits Problems                                 | Page 366 Page 370 Page 375 Page 377                                  |

|                                              | CHAPTER 17 PAGE 378                                                                                                                                          |                                                                      |

|                                              |                                                                                                                                                              |                                                                      |

|                                              | Circuits for Timing                                                                                                                                          |                                                                      |

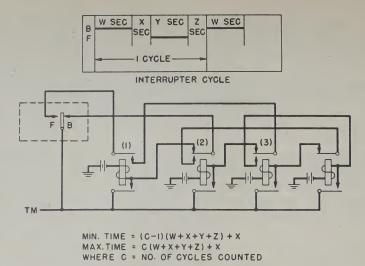

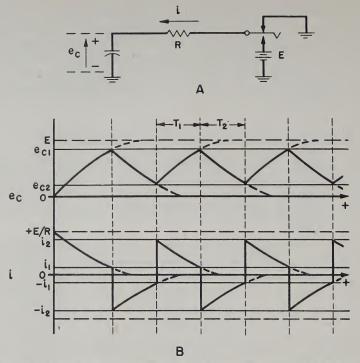

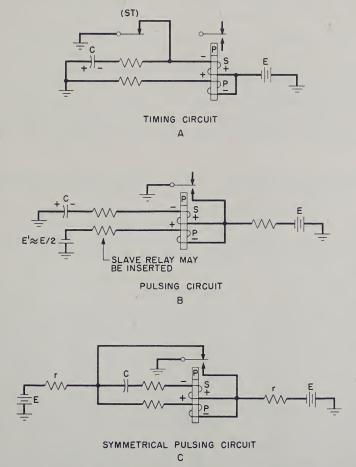

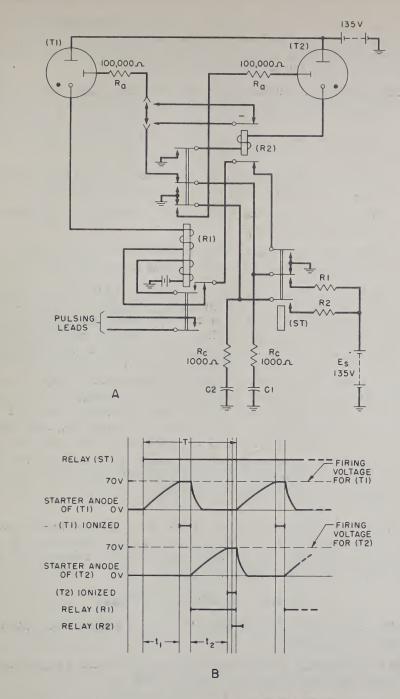

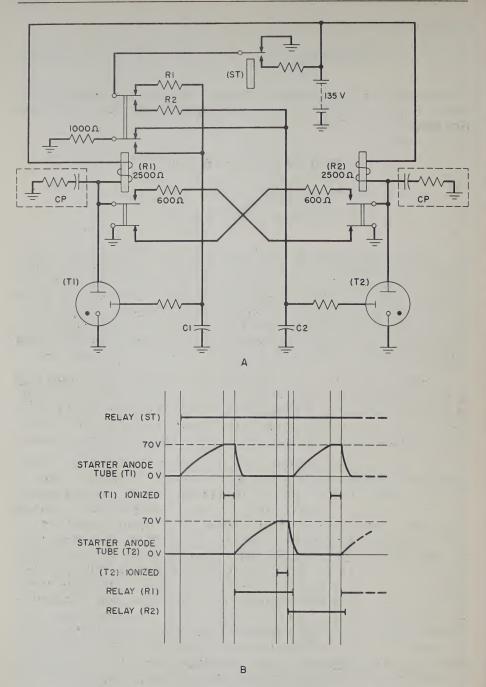

| 17.1<br>17.2<br>17.3<br>17.4                 | Standard Slow-Acting Relays Interrupter Timing Circuits Capacitor-Timed Relays Gas-Tube Timing Circuits Problems                                             | Page 379 Page 381 Page 383 Page 395 Page 404                         |

|                                              | CHAPTER 18 PAGE 405                                                                                                                                          |                                                                      |

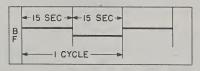

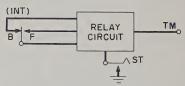

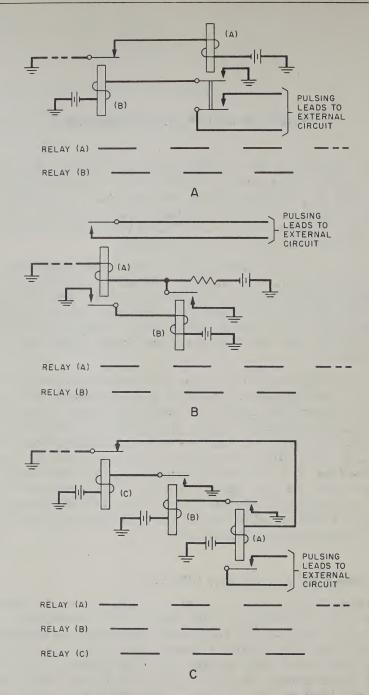

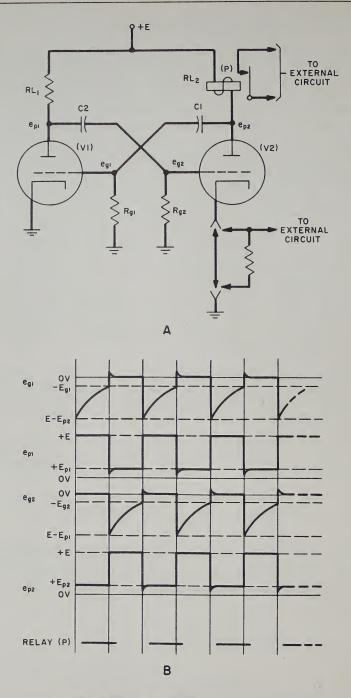

|                                              | Circuits for Pulse Generation                                                                                                                                |                                                                      |

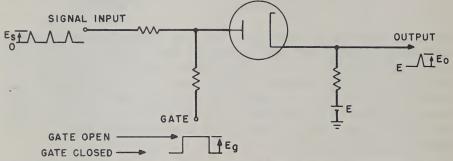

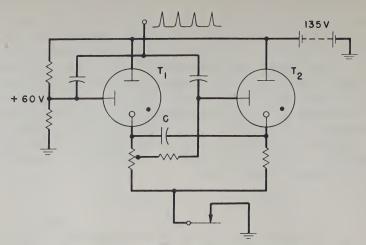

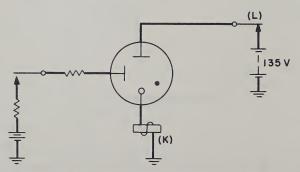

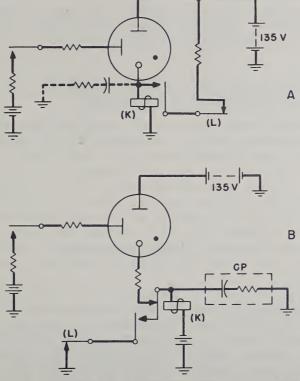

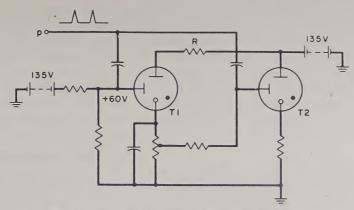

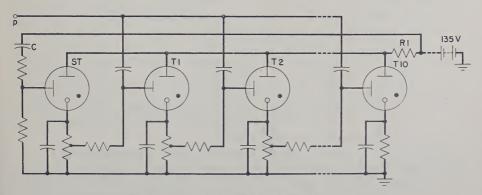

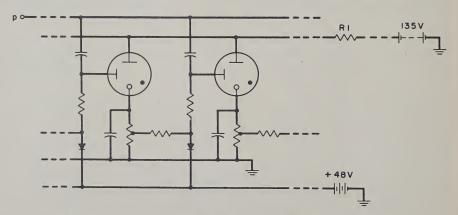

| 8.1<br>8.2<br>8.3<br>8.4<br>8.5              | Simple Relay Pulsing Circuits Capacitor-Timed Relay Pulse Generators Gas-Tube Pulsing Circuits Vacuum-Tube Pulsing Circuits Pulse Detection Problem          | Page 405<br>Page 407<br>Page 414<br>Page 419<br>Page 421<br>Page 422 |

|                                              | CHAPTER 19 PAGE 423                                                                                                                                          |                                                                      |

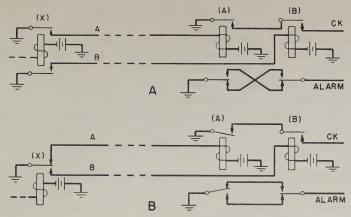

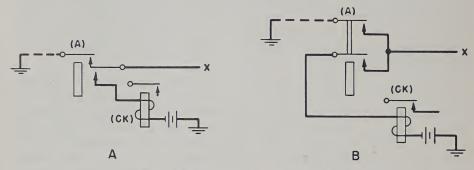

|                                              | Circuits for Checking                                                                                                                                        |                                                                      |

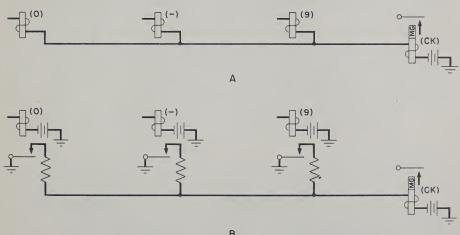

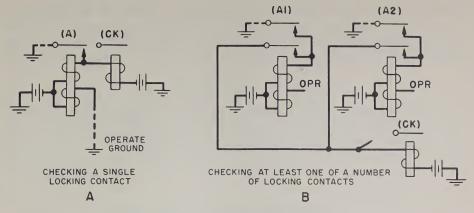

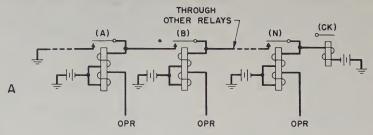

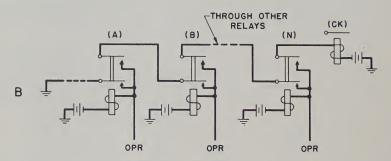

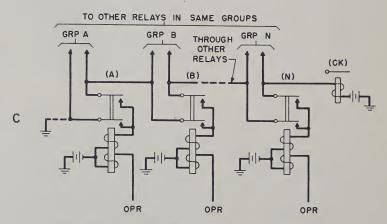

| 9.1<br>9.2<br>9.3<br>9.4                     | Affirmative and Negative Check Principles  Probability-Type Checking.  Checking Single Relays and Contacts  Checks for Opens, Grounds, and Crosses  Problems | Page 425<br>Page 427<br>Page 432<br>Page 437<br>Page 443             |

|                                              | CHAPTER 20 PAGE 446                                                                                                                                          |                                                                      |

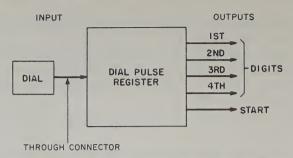

|                                              | Circuits for Registration                                                                                                                                    |                                                                      |

| 20.1<br>20.2<br>20.3<br>20.4<br>20.5<br>20.6 | Types of Register Elements                                                                                                                                   | Page 446 Page 448 Page 449 Page 451 Page 454 Page 456 Page 459       |

|       | CHAPTER 21 PAGE 460                                  |           |

|-------|------------------------------------------------------|-----------|

|       | Circuits for Calculating                             |           |

| 21.1  | Codes                                                | Page 461  |

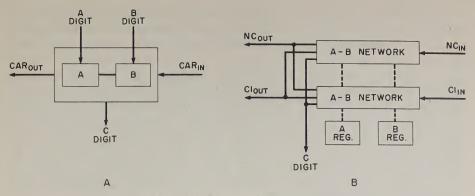

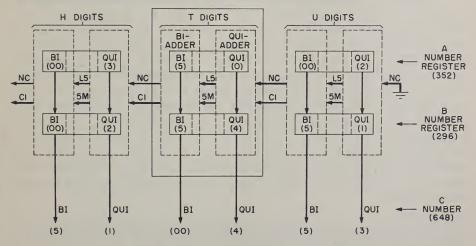

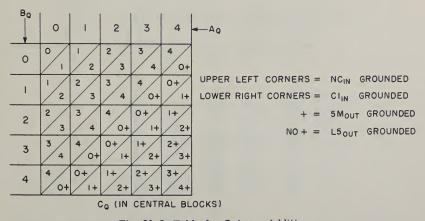

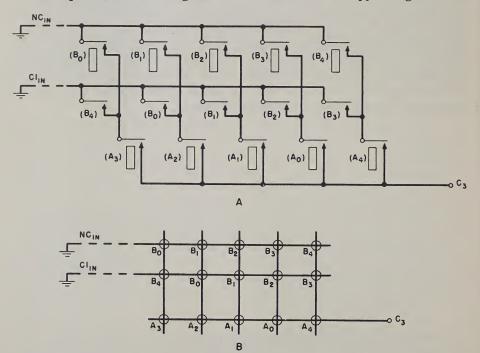

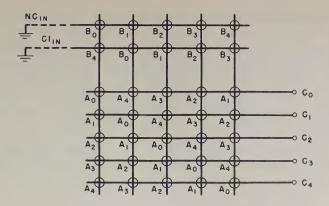

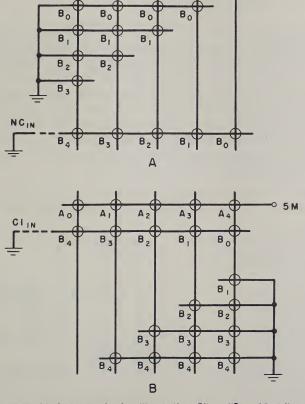

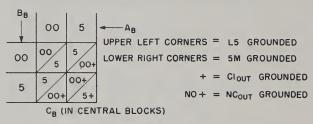

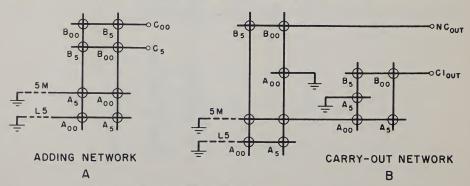

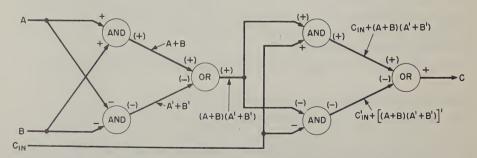

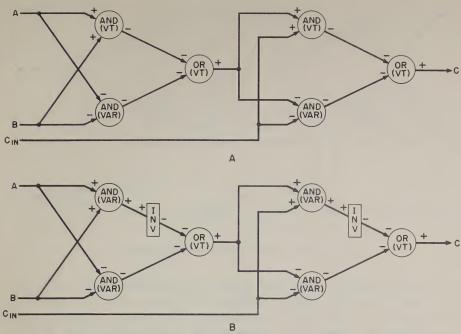

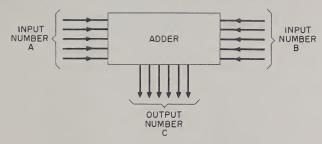

| 21.2  | Addition                                             | Page 462  |

| 21.3  | Subtraction                                          | Page 472  |

| 21.4  | Multiplication                                       | Page 474  |

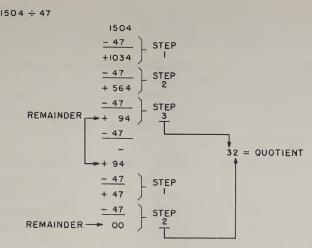

| 21.5  | Division                                             | Page 483  |

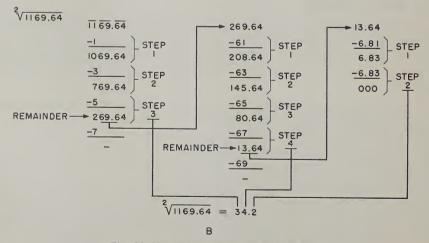

| 21.6  | Square Roots                                         | Page 485  |

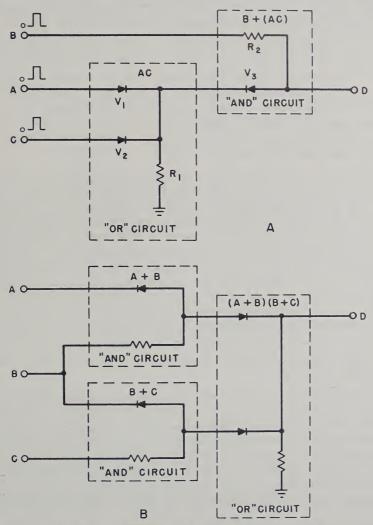

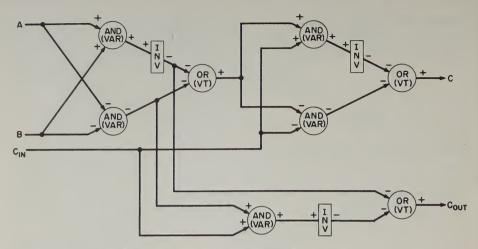

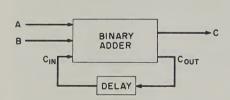

| 21.7  | Design of an Electronic Binary Adder                 | Page 487  |

| 21.8  | Appendix I: N <sup>2</sup> as a Sum of Factors       | Page 493  |

| 21.9  | Appendix II: Determination of Square Roots           | 1 460 100 |

|       | by Repeated Subtraction                              | Page 493  |

|       | Problems                                             | Page 495  |

|       | CHAPTER 22 PAGE 496                                  |           |

|       | CHAPTER 22 PAGE 496                                  |           |

|       | General Principles of Multifunctional Circuit Design |           |

| 22.1  | Circuit Requirements                                 | Page 497  |

| 22.2  | Underlying Factors                                   | Page 498  |

| 22.3  | The Four Stages of Design                            | Page 500  |

|       |                                                      |           |

|       | CHAPTER 23 PAGE 506                                  |           |

|       | Planning a Multifunctional Circuit                   |           |

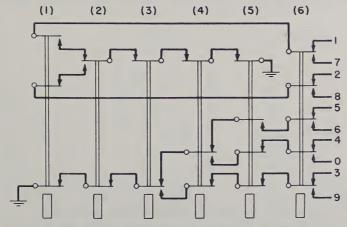

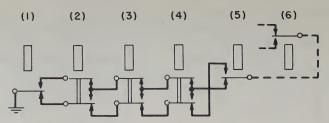

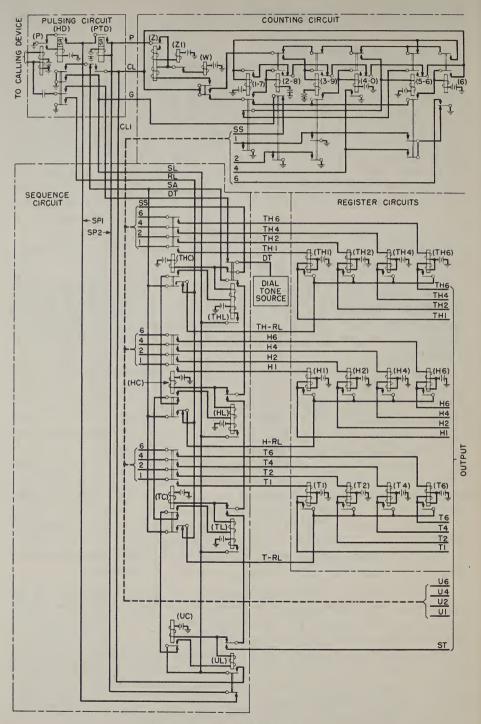

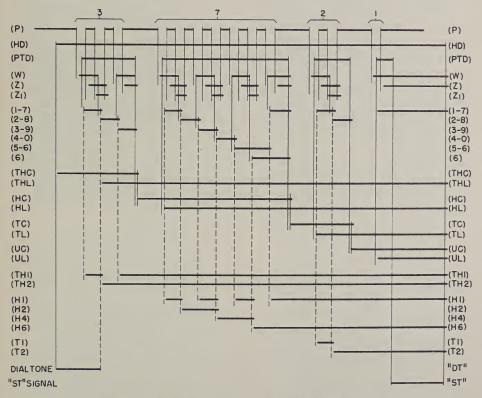

| 23.1  | Statement of the Problem                             | Page 506  |

| 23.2  | Detailed Requirements                                | Page 508  |

| 23.3  | Preliminary Planning                                 | Page 509  |

| 23.4  | Developing the Block Diagram                         | Page 515  |

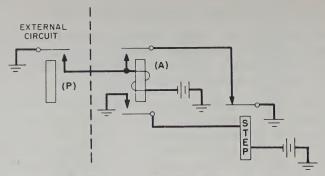

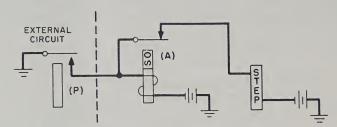

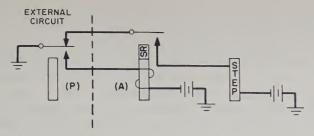

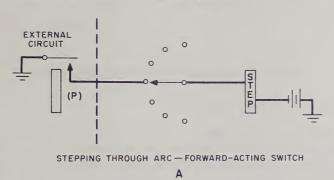

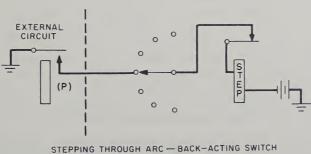

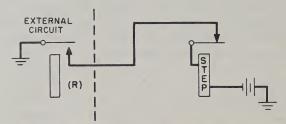

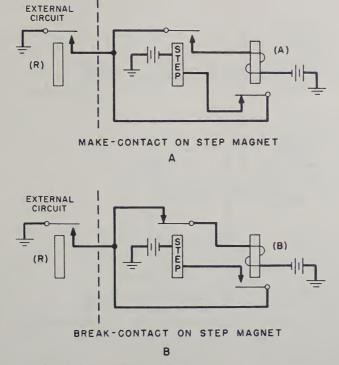

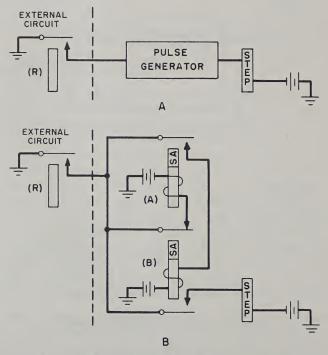

|       |                                                      | - mg- one |

|       | CHAPTER 24 PAGE 523                                  |           |

|       | Detailed Design of a Multifunctional Circuit         |           |

|       | Detailed Design of a Multifunctional Circuit         |           |

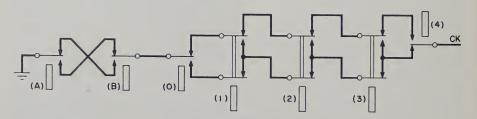

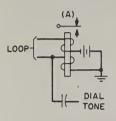

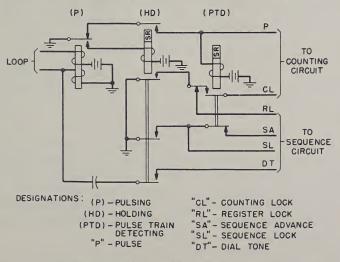

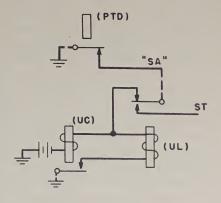

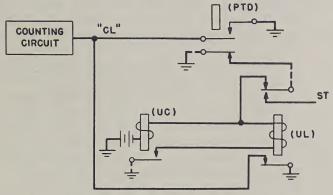

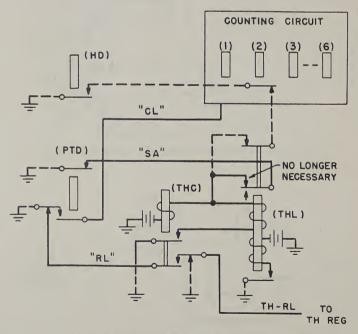

| 24.1  | Pulse Repeating, Pulse-Train Detecting,              |           |

| 0.4.6 | and Supervisory Holding Circuits                     | Page 524  |

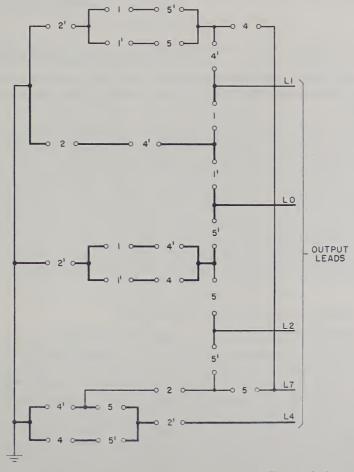

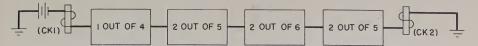

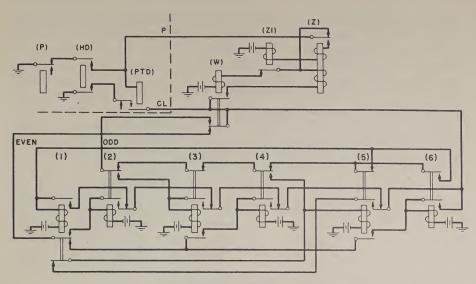

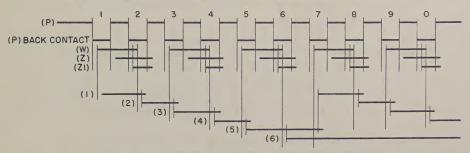

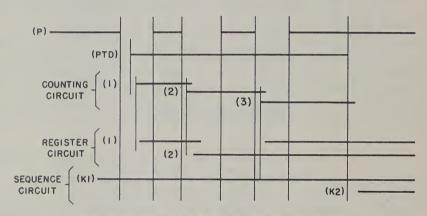

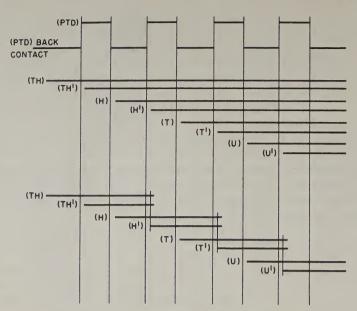

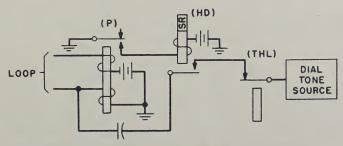

| 24.2  | The Counting Circuit.                                | Page 527  |

| 24.3  | The Register Circuit                                 | Page 531  |

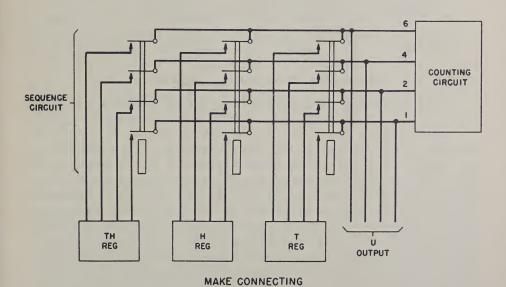

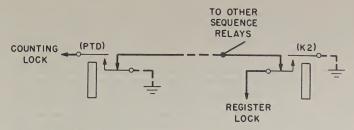

| 24.4  | The Sequence-Connecting Circuit                      | Page 532  |

| 24.5  | The Minor Functions                                  | Page 539  |

| 24.6  | Conclusion                                           | Page 545  |

### Chapter 1

### FUNDAMENTAL CONTROL CONCEPTS

From a technological point of view, one of the most striking aspects of the present period of human endeavor is the emergence of machines that handle information automatically. In more graphic but less accurate terms, these are machines that "think". With every passing day, not only scientists and engineers but the general public as well are becoming more aware of complex devices or systems that can accept information in one form or another, correlate and digest this information, and arrive at logical conclusions. Mechanisms of this nature are broadly classified as "automatic control systems."

Automatic control systems break down into two distinctly different subdivisions: those that function on the basis of continuous input data, or data that vary smoothly from one value to another; and those that function on the basis of data that vary in discrete steps. The subject of this book is the design of circuits for systems of the latter class, properly known as "switching" systems. Among the more spectacular and well-known examples of such systems are the modern large-scale digital computers and the automatic telephone switching systems. Both of these systems accept information in numerical form and produce output results that are precisely related to the input data.

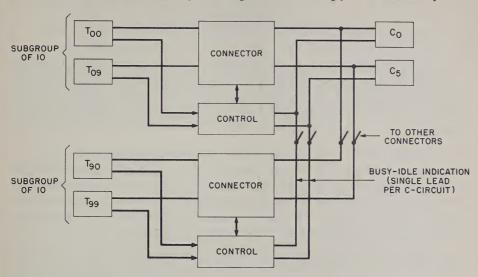

The nature of a switching system and its component circuits can perhaps be more clearly illustrated than defined. Modern dial telephone systems are an example. The machinery of a central office contains a network of switching devices by means of which subscriber lines and trunks can be interconnected. Centralized control circuits are provided to control the actions necessary in establishing a connection. These control circuits may range in size from less than a dozen switching elements to a thousand or more. The system is controlled by instructions from the subscriber which consist of a series of pulses generated when a number is dialed. These signals start an intricate train of reactions which are determined in part by the information received from the subscriber, in part by information collected within the system concerning busy and idle path conditions, and finally by built-in knowledge. This knowledge is placed there by the designer who analyzed a large number of control situations, determined suitable plans of action, and developed switching circuits to carry out these plans.

A variety of actions are performed. The dial pulses are counted as they arrive and the information is stored as numerical digits in coded form, to be used as required. Various circuit units are interconnected with each other to cooperate in the control. Trunks and interconnecting linkages are selected in groups and tested for busy and idle conditions. On its own initiative a control circuit can pick an idle path from a large group or, if all are busy, can choose an alternate group or make other disposition of the call, such as returning a busy signal. Centralized control circuits can operate any switch in the office used for interconnecting subscriber lines and trunks, and can locate suitable switches for a given call. After a control circuit has completed its action, it will restore itself to a normal condition and be available for use on another call.

During this entire process, information, either received as input data or held as stored data, is recorded, translated, manipulated, transmitted, etc., as discrete digital items. For any set of inputs, there is a corresponding logical and invariable output condition or group of alternative output conditions (for instance, a connection to a busy-tone source instead of the called line, if the line is busy).

Other examples can be cited to illustrate the varying facets of switching systems, ranging from relatively simple machine controls up through such complex mechanisms as automatic accounting systems and inventory control systems. The latter type of system, for instance, can store information on the complete inventory of a business enterprise, be it a department store, factory, warehouse, or airline. Each inventory item is assigned an identifying code, and with it is associated the present status or quantity of the item. The system can answer requests from key equipments at local or remote points as to the current state of any stock item, and can change information automatically, by subtraction in accordance with filled orders or by addition in accordance with cancellations or new purchases.

In all these switching systems, the internal circuitry that relates input to output consists of paths interconnecting discrete-valued apparatus elements. Well-known examples of this type of apparatus are electromagnetic relays, electromagnetic switches, rectifiers, gas-filled electronic tubes, magnetic tapes and drums, mercury delay-lines, and certain arrangements of vacuum tubes. The action of any of these elements in switching circuits is to open or close, or switch, interconnecting paths, or to establish definite conditions over them, in predetermined logical patterns which are ordered by the input information. The outputs generated by a system as a whole may consist of pure information, as a printed page of figures in a computer; control signals, as the motor on-off signals in an elevator system; or a particular

state of the system, as the establishment of a new talking channel in a telephone office.

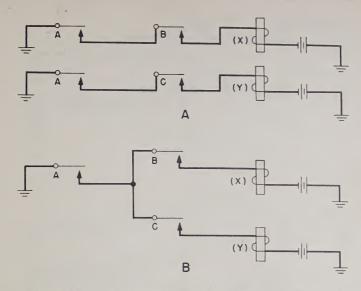

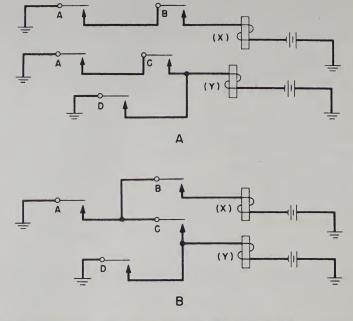

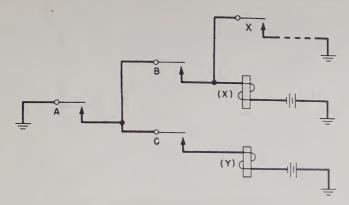

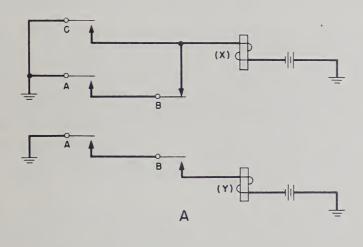

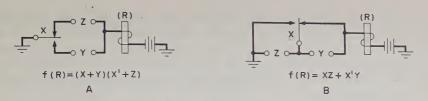

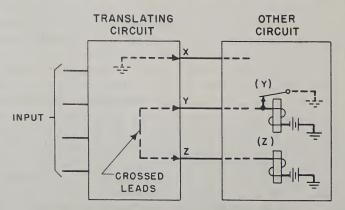

The concept of logic is the most noteworthy aspect of switching circuits; in fact, the schematic representation of a relay circuit is a symbolic expression of a set of conditions and their logical conclusion. For example, the configuration of a circuit is largely determined by logical relationships of the form: output X should be closed when inputs A and B occur simultaneously; output Y should be closed when input A occurs before input B; output Z should be closed when either input A or input B occurs. Methods of determining logical relationships from statements of requirements, and the developing of circuits to conform to the logic, form a principal part of this volume.\* Furthermore. it will be seen that the terminology and procedures of formal logic are of great assistance in designing circuits. From this point of view, it is not difficult to see that there is some validity to the feeling that machines designed on such a basis "think." Note, however, that the thought processes are in all cases built into the machine and that the machine at most merely reproduces the original plans of the designer.

The preceding discussion indicates that there is a vast ultimate field of application for switching circuits, for not only are many control situations subject to logical treatment, but they are inherently discrete or numerical in nature, or can be transposed into this form by suitable detecting and converting devices.

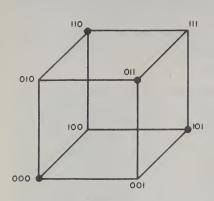

The ability of switching circuits to perform complex as well as simple functions by means of relatively simple apparatus elements is based upon the combinations into which the apparatus elements of the circuits can be manipulated. Any individual combination of several elements can be made to give a unique indication by suitable interconnections. If apparatus elements that can assume any one of five states or 'values' are used, one element can indicate five conditions; two elements, twenty-five conditions; three elements, one hundred and twenty-five conditions; etc. If apparatus elements with only two values are used, the same effects are evident. For example, a group of twenty such two-valued elements can be set into more than a million unique combinations.

It can be seen almost intuitively that the simplest and most elemental control conditions are two-valued, that is, they are "on" or "off", "positive" or "negative", "open" or "closed". Indeed, in a sense, it is straining for complication to go beyond two values for control purposes,

<sup>\*</sup> An understanding of the electrical basis of circuits is assumed, for the most part, and this phase of the subject is not stressed.

since marginal conditions and tolerance limits increasingly difficult to meet are thereby introduced. Since it is natural to match the apparatus to the most effective control conditions, the use of two-valued apparatus for switching applications is clearly indicated. Even with this restricted number of values or states per apparatus element, the rate at which the distinct combinations of elements increases with the number of elements permits the handling of the most complex requirements with a relatively small quantity of apparatus.

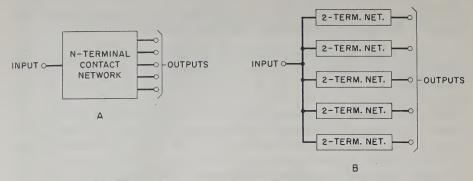

Multi-valued apparatus, such as a multi-terminal electromagnetic switch, is useful in certain special applications in switching circuits. Although there may be a multiplicity of paths through the device, individually the paths are either opened or closed during operation and the apparatus may be analyzed essentially on a two-valued basis. Control of the device is also usually two-valued, consisting either of a repetition of signals over one lead or combinations of on-off signals over several leads. The multi-valued device can normally be considered as an aggregation of two-valued devices, constructed in a package for reasons of economy or convenience. Since it is designed for specialized applications, it does not offer the circuit flexibility inherent in two-valued apparatus. Therefore the major effort in this volume is devoted to the design of circuits employing two-valued elements.

An important characteristic of switching circuitry is that it can be made to hold or retain a given state after the excitation that produced the state has passed. This is the factor of memory which permits switching circuits to respond to a sequence or time-order of input intelligence, and eliminates the necessity of an input path to each apparatus element in a circuit. An example of the utility of this concept is furnished in the association of a telephone switching office and a subscriber by means of a pair of wires. Over this path, by a sequence of identical signals, the subscriber can control the connection of his line with any one of millions of other subscribers.

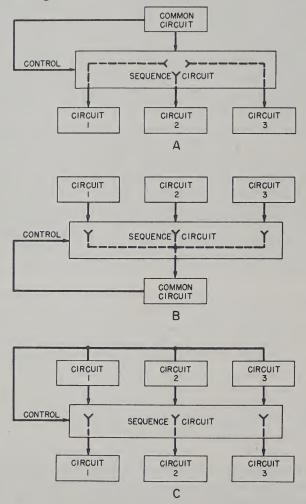

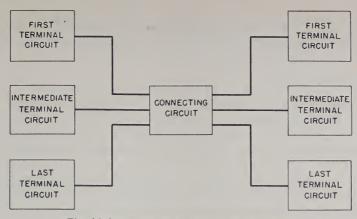

The remarks up to now have been general and do not give a clear picture, in a detailed sense, of what switching circuits do. And in this introduction it is not essential to point out the many simple control functions, where effect is obviously related to cause, that circuits of this type can be designed to handle effectively. However, large circuits or systems, involving dozens or hundreds of apparatus elements and performing intricate combinations of control functions, deserve further consideration. Circuits of this type are inevitably composed of many interrelated sub-circuits, each of which performs one or a small number of individual functions. These sub-circuits can be considered as the true building blocks of major switching circuits. Design of a large circuit or a system, then, consists of determining from the requirements

of the problem the basic and individual functions which are necessitated by circuit logic; designing circuits to perform these basic functions; and finally, integrating or coordinating the functional circuits into the complete system. In the final system, information received from the outside over input channels is recorded and interpreted, decisions are made as to what functional circuits should be called into play, internal information is passed back and forth between circuits, checks are made as to accuracy and validity of performance, and finally output signals or actions appear.

Surprisingly, even in a large and complete switching system the majority of switching circuit requirements can be met by a relatively small number of types of functional circuit. Within each type, of course, there are many variations, some due to detailed requirements and some to the whim of the designer. The names of the types of circuit give an immediate clue to the kind of action each performs. Only a few examples are mentioned here; later chapters describe most of the types of circuit in detail.

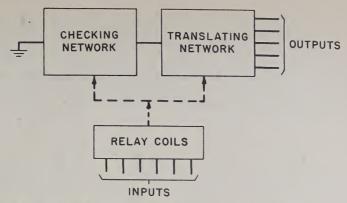

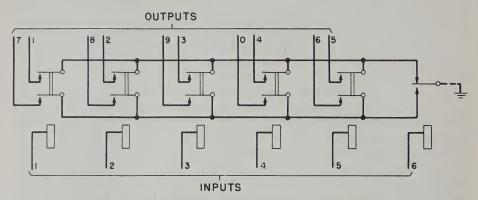

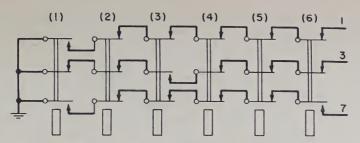

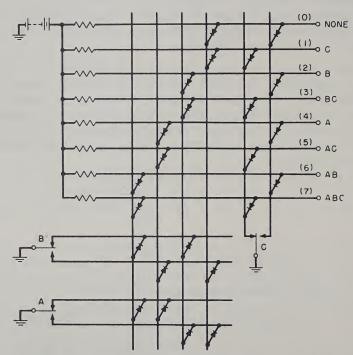

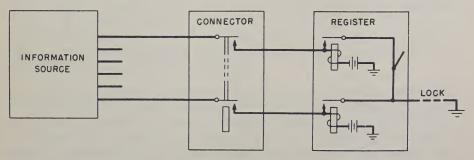

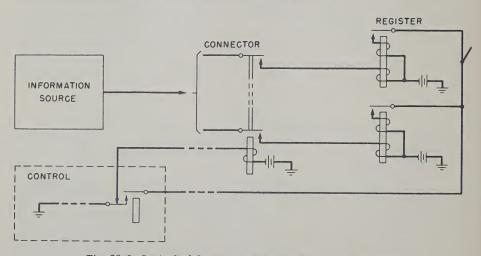

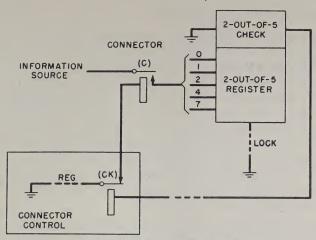

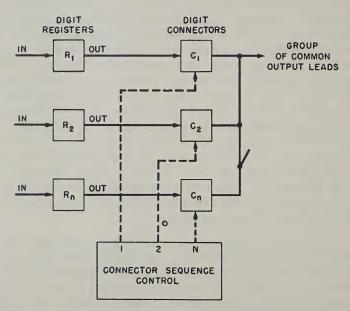

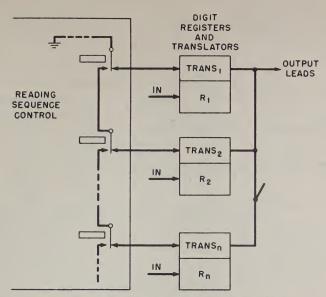

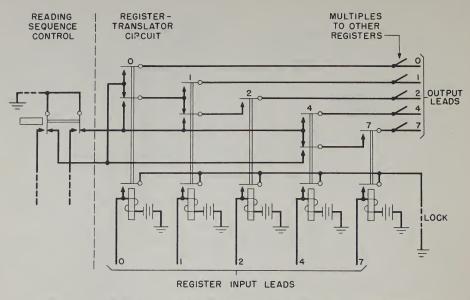

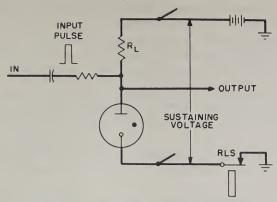

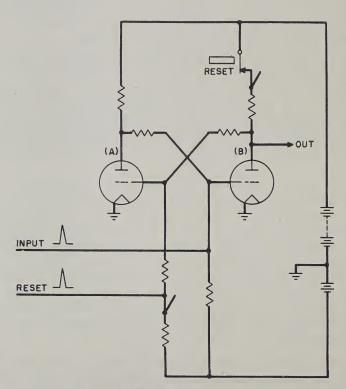

A simple basic circuit is the "register" circuit which records and holds information until required by another functional circuit. The particular configuration of the register circuit depends upon the form or code in which the information is made available. Often associated with the register circuit is the "translating" circuit which converts information from one code to a different code. It is often convenient to receive or record information in a particular code, whereas a different form is required for use or transmittal to other parts of the system.

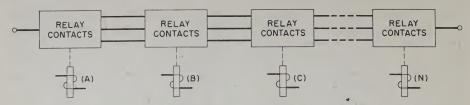

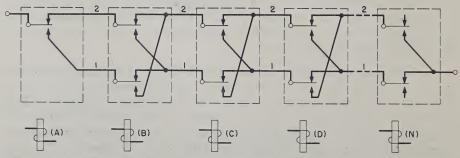

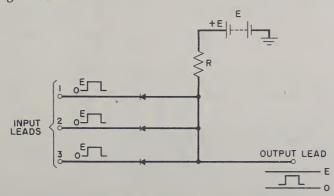

Information is often sent on a repetitive pulse basis, and to receive it a "counting" circuit is necessary. The counting circuit is actuated by successive pulses and can be arranged to count either a definite number of pulses or to give a distinct indication corresponding to each individual pulse. This circuit is also of use in keeping track of a series of events.

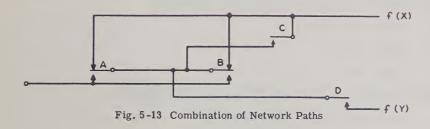

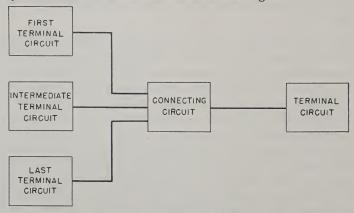

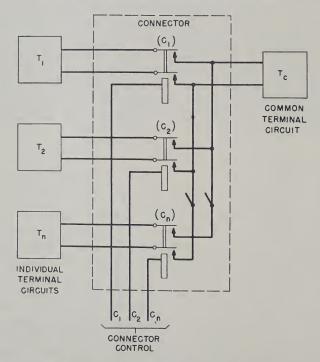

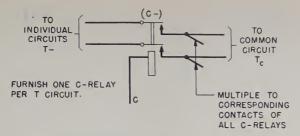

In most multi-functional circuits, there is need for "connecting" circuits to associate functional parts for short periods or to connect to circuit inputs and outputs. There are many types of connecting circuits, with the differences dependent upon the number of connectable circuits, the duration of individual connections, and the number of leads required.

Often associated with connecting circuits are the 'locating' circuits which are used to choose one item out of many. Classified under locating circuits are 'selecting' circuits, which pick one item from many on a predetermined basis; 'hunting' circuits, which pick any available one from several identical items; and 'finding' circuits, which identify a particular item that requires service.

The "lock-out" circuit is used to regulate the flow of traffic among the parts of a complex system. Its usual function is to permit but one out of several competing items to act or to have access to a common part of the system.

Functional circuits that have less general application than the preceding ones are the "calculating" circuits. These are circuits which perform the basic arithmetical functions of adding, subtracting, multiplying, and dividing. Their chief application is in calculating or computing systems.

This partial list of basic functional switching circuits serves to give an idea of the types of action of which switching circuits are capable in control applications. As mentioned, these circuits have little utility individually, but are the functional building blocks from which complete systems are constructed.

It has already been stated that two-valued apparatus elements are at present considered the best devices for general use in automatic control circuits of the switching type. Where multi-valued elements are used, it is in specific applications where economy or efficiency can be achieved by, in effect, combining several two-valued elements into a single piece of apparatus. Among the two-valued elements, the leading contenders for use in existing switching circuits are electromagnetic relays, hot- or cold-cathode gas tubes, and vacuum tubes connected to act as two-valued devices. Other discrete-valued devices which are appearing in switching circuits at an accelerating rate are varistors, transistors, and magnetic recording devices.

Each of these devices has specific characteristics which peculiarly suit it to certain applications in the switching field. An instance of this appears in the requirement for extreme speed, in the microsecond range, which sometimes arises. This inevitably drives the designer to the use of vacuum tubes or the semiconductors. However, as a general tool for the majority of switching applications, the electromagnetic relay has as yet no peer.

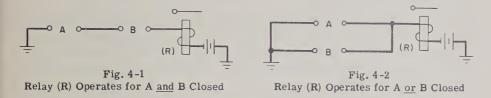

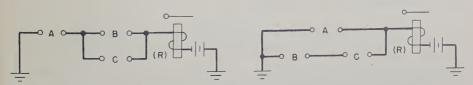

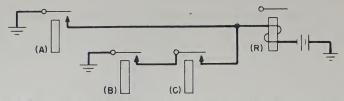

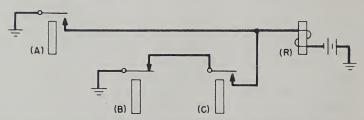

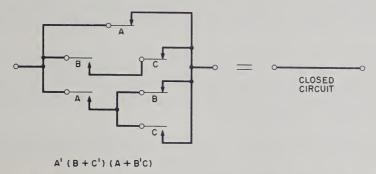

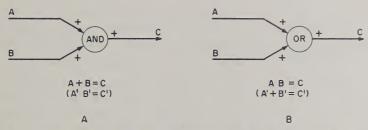

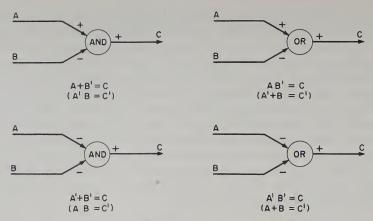

Of major importance in this respect is the manner in which the relay indicates its state. This is by means of contacts that may be used in circuit paths which are completely independent, electrically, of the relay operating path. These contacts may be open or closed when the relay is unoperated, and will be in the inverse state when the relay is operated. By placing the contacts of several relays in series, any conclusion requiring a coincidence of conditions can be indicated. By connecting contacts in parallel, a conclusion dependent upon the existence of any one or more conditions out of many can be indicated. In logic, these two alternative sets of conditions would be known as "and" and

"or" requirements. By suitable interconnections, any conceivable combination of "and" - "or" relationships can be expressed with a relay contact network. Of equal importance with this concept is the fact that use of normally open and normally closed contacts permits specifying not only the inclusion, but also the exclusion, of dependent conditions.

These considerations make the relay an excellent instrumentality for expressing the logical relationships which are the very basis of switching problems. A secondary factor, which has considerable practical importance, is the fundamental simplicity of the relay as a circuit element. Although the interconnecting paths of a multi-relay circuit viewed as a whole may become highly complex, the control network for each individual relay forms a simple open or closed path which rarely requires additional apparatus for correct functioning. Physically, the relay is easy to comprehend, even though a great deal of knowledge and ingenuity has entered into its design. From the circuit point of view, in most applications the relay is simply a device which opens or closes a multiplicity of paths when power is applied to it, and performs the inverse operation on the paths when power is removed.

The importance of this simplicity should not be underestimated. It enables the circuit designer to concentrate on the logical aspects of any set of circuit requirements rather than be diverted by essentially extraneous problems of making the circuit elements perform in a particular manner. A natural consequence of this is that the designer has greater freedom in dealing with the logical aspects of a switching problem when working with relays than with any other type of circuit element. This is a general statement, and does not exclude the choice of other apparatus elements when their characteristics match the requirements of a particular problem.

The relay in a general sense has other attributes which contribute to its utility and flexibility as a circuit tool. Its operating time, depending upon construction, ranges from a minimum of a few milliseconds up to about one second, with more extreme values available in special relays. It has seen such extensive use over many years that it is today a highly-developed and reliable device. Of utmost importance is the fact that it is widely available in a great variety of types that offer almost complete freedom in the choice of the correct relay for each particular application.

In view of these considerations, the major portion of this volume is devoted to the design of typical relay circuits. There is less loss of generality in this treatment than might appear, however, since the same fundamental logic is applicable to all types of two-valued switching apparatus. The differences in approach to electronic circuits, for instance, arise in the application of detailed design techniques rather than in

general principles. In order to indicate the nature of these differences, selected examples of electronic switching design techniques are incorporated in the text, and tube circuits performing functions comparable to relay circuits are presented. Some basic circuits for control of multi-terminal switches are also included for the same reason.

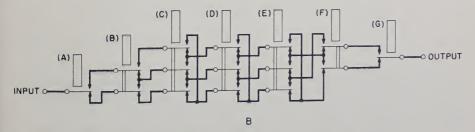

In presenting the subject of this volume, the objective is to progress from the basic design concepts up through the design of relatively complex multifunctional circuits. Although no formal division is made, the text can be considered as falling into three parts: basic relay circuit design fundamentals; the design of single-function circuits; and the planning and design of multifunctional circuits.

## Chapter 2

#### SWITCHING APPARATUS

It has been noted in Chapter 1 that the design of switching circuits consists primarily of analyzing the functional circuit requirements in terms of two-valued conditions, and devising logical interrelationships of circuit paths and apparatus to meet the conditions. The choice of apparatus to use in the circuit is in a sense a separate problem which can often be met after the basic circuit design has been completed. This is particularly true with relay circuits, and to a lesser extent with circuits using electronic apparatus.

Since this volume is primarily concerned with the fundamentals of relay circuit design, little detailed study of apparatus is included. However, this chapter will discuss the basic characteristics of relays as circuit elements in order that the circuit design chapters need not be interrupted by digressions on the physical aspects of apparatus. Also, the schematic conventions and the vocabulary used in relay circuit design will be given. On the other hand, it will be more convenient to give the comparable description of switches and electronic circuit elements in the chapters devoted to their circuit use. This will be done since the circuit design using such apparatus is more intimately related to the apparatus than is true with relays.

In addition, this chapter will mention some types of apparatus such as keys, plugs, and jacks, which are useful adjuncts to circuits. In all cases descriptions will be general since detailed information can be found in manufacturers' specifications and catalogues.

A relay is essentially a remotely controlled switch which can open or close contacts when suitable electrical conditions are met. From a circuit point of view, relays can be divided into two broad classes, known as general-purpose relays and special-purpose relays. The general-purpose relay, often called a telephone-type relay, is the work-horse in relay switching circuits around which is constructed the major portion of switching circuitry. In its usual form it is a direct-current relay operating in a voltage range of a few volts to approximately 100 volts\*. In order to be a flexible tool, the general-purpose relay provides a basic structure on which can be placed a variety of

<sup>\*</sup> The most common voltage in telephone central offices, for instance, is 48 volts.

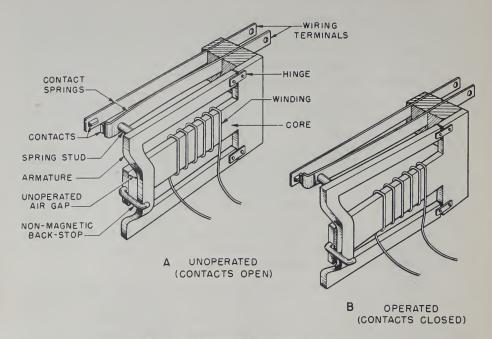

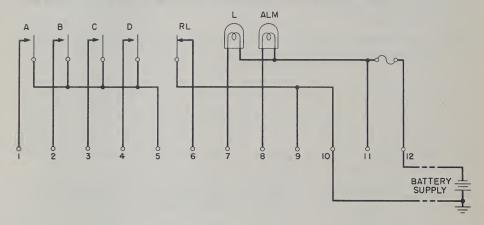

Fig. 2-1 Essential Features of a Relay

contact combinations and a variety of winding combinations to meet different operating conditions. The contacts in general carry only moderate currents (1.0 ampere or less), primarily for controlling other relays. The acting times of these relays range from a few milliseconds to several hundred milliseconds.

The special-purpose relay, on the other hand, is usually designed for a particular type of application, and will vary in construction and appearance depending upon its function. Its attributes may be extreme speed, high sensitivity, polarized operation, operation on alternating current, contacts of very heavy load-carrying capacity, etc.

#### 2.1 GENERAL-PURPOSE RELAYS

All electromagnetic relays are composed of the same three basic parts: a magnetic structure or framework, a winding, and a set of contacts mounted on springs. The winding and the magnetic structure convert electric power into mechanical action; and the set of contacts, driven by the resultant motion, open and close external circuit paths. The general relation of parts is shown on Fig. 2-1.

The magnetic structure consists of a core, one or two polepieces, and a movable armature hinged to the rear pole-piece, often called the heel-piece. All these parts are made of soft iron or other magnetic material, and form a closed magnetic circuit except for an air gap between the free end of the armature and either a front polepiece or the core itself. When the relay is energized, the pull is concentrated in the air gap, and the armature moves to close the gap.

The relay winding (or windings) is placed on the core of the structure, and the winding ends are brought out to connecting terminals. The pull developed at the armature is a function of the current, the number of winding turns, the air gap, and the magnetic material and structure.

The relay springs carrying the contacts are usually clamped to the structure at one end and are free to move at the other. There are two sets of springs, one set relatively stiff and fixed in position, the other set relatively flexible and linked to the armature through insulating studs or a comb arrangement. Precious-metal contacts are attached to the mating surfaces of the springs. When the armature moves, the contacts either open or close, depending upon their initial condition.

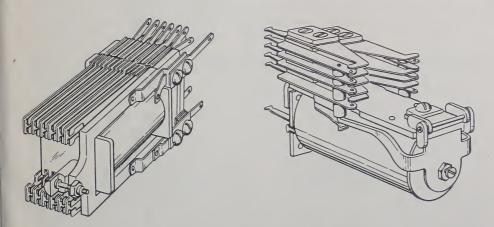

Although all general-purpose relays conform in these fundamental aspects, the construction and appearance of different relays vary in accordance with the manufacturer's design objectives and concepts of efficiency and performance. Two representative types of general-purpose relays are shown on Fig. 2-2. In service, they mount in horizontal positions on flat metal plates, usually with the moving parts in a vertical plane to avoid the effects of gravity.

In considering the general purpose relay from the circuit point of view, the important aspects of the device are: the contact or spring

Fig. 2-2 Typical General-Purpose Relays

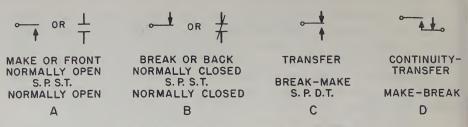

Fig. 2-3 Basic Relay Spring Combinations

combinations; the winding combinations; the power requirements; the acting speeds; and the contact current load capabilities. The magnetic structure of the relay is of primary interest only in an indirect sense, because of its effect upon the power and speed capabilities. However, modifications of the basic relay structure to affect its speed characteristics are important. These various aspects of the relay will be taken up in the following paragraphs.

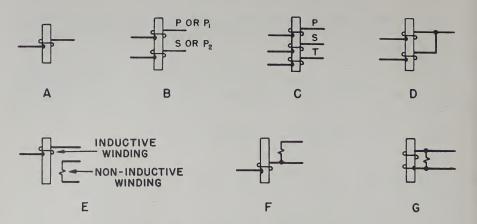

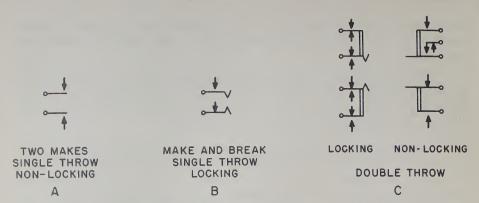

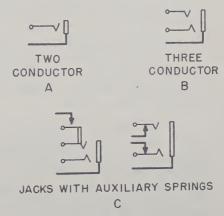

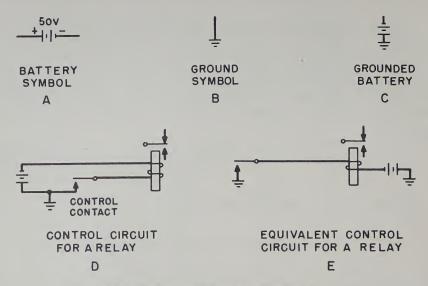

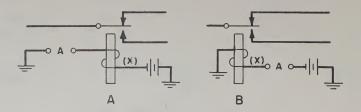

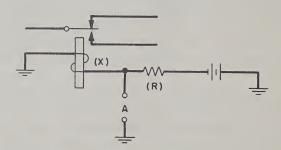

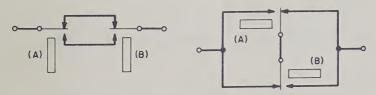

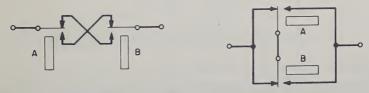

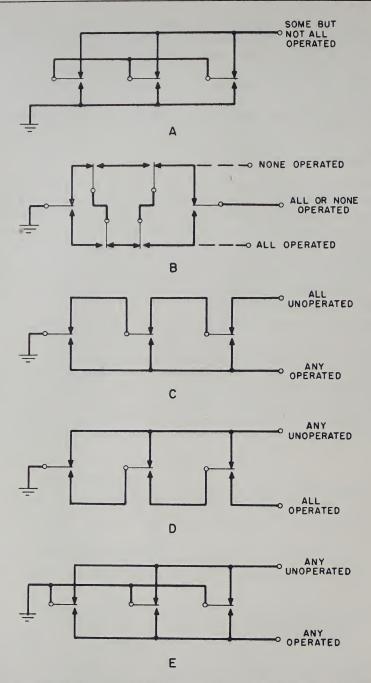

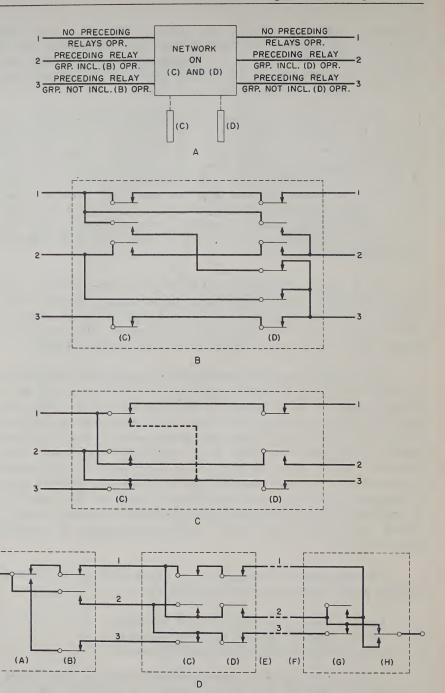

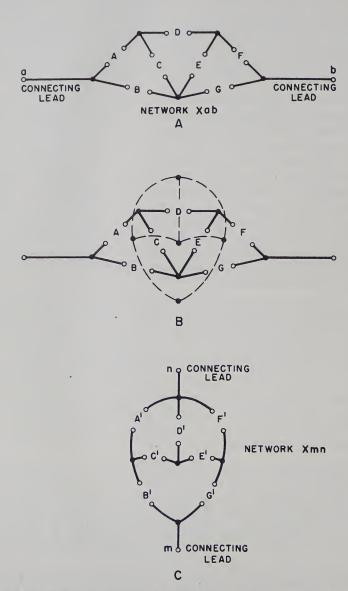

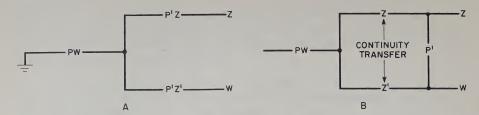

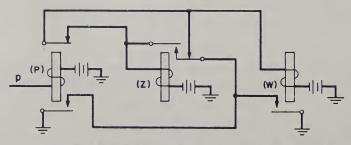

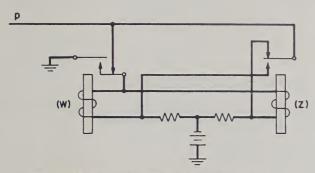

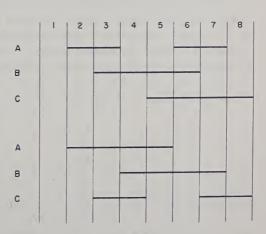

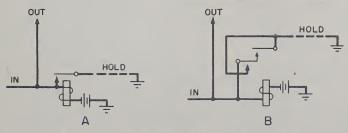

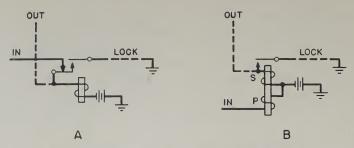

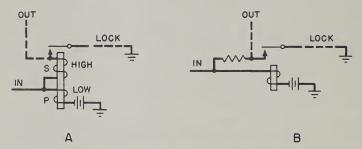

Spring Combinations. The two basic relay spring combinations are the "make" and the "break" combinations. These are illustrated in Figs. 2-3A and 2-3B in two standard schematic forms. In this text, the first form shown, which is the communications standard, will be used exclusively. On the figure, alternate acceptable designations are also given in addition to make and break. Two other very common spring combinations, the "transfer" and the "continuity-transfer" or "continuity", are shown as Figs. 2-3C and 2-3D. The transfer normally has the property of opening the break contact before closing the make contact, whereas the continuity insures a make-before-break contact sequence.

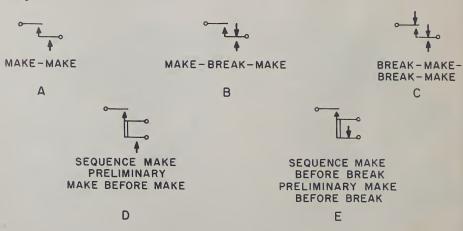

Fig. 2-4 Specialized Spring Combinations

Examples of more specialized spring combinations are shown on Fig. 2-4. In general, these are less universally used than the combinations of Fig. 2-3.

Several spring combinations may be grouped on an individual relay in one or more assemblies. The maximum allowable number of individual springs varies with the type of general purpose relay, but

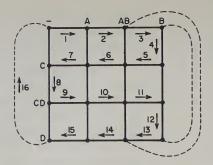

usually does not much exceed 24. A large number of different spring arrangements utilizing the basic combinations are, of course, possible. A typical example in two separate spring assemblies is shown associated with the schematic representation of a relay core on Fig. 2-5. The individual springs are often numbered in accordance with either the order of wiring terminals in back or the order of springs viewed from the front.

Relays are also available with a large number, of the order of 50 or 60, of single-type springs, such as make contacts. These are somewhat out of the category of general purpose relays, and are often designated multi-contact relays.

Fig. 2-5 Spring Combinations Associated with Relay Core

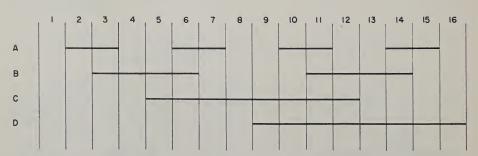

Windings and Winding Arrangements. General-purpose relays are available with a variety of different windings and combinations of two or more separate windings. The effect of the number of turns and the resistance of particular windings will be discussed in the section on operating characteristics; in this section, only the various winding arrangements will be covered.

The most common winding arrangement is the single winding shown on Fig. 2-6A. The semi-circular dot on the winding symbol indicates the inner end, or the end of the winding closest to the core. Following the single winding in utility is the double winding, shown on Fig. 2-6B, in which the two windings are often designated primary and secondary. In this and other multi-winding cases, the dots can be interpreted to give the directional sense of the windings in order to simplify the making of aiding or opposing connections. Double windings are prepared in a variety of ways, of which the simplest is to place one winding directly on top of the other. This permits the utmost flexibility in providing windings completely independent in characteristics. Other methods of construction may be employed when it is necessary to

Fig. 2-6 Relay Winding Arrangements

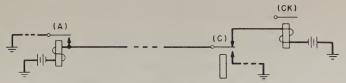

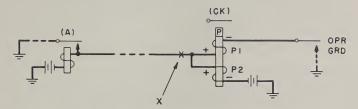

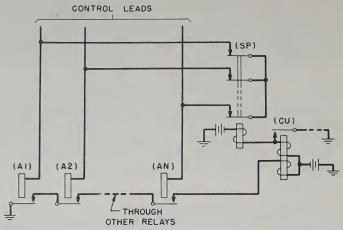

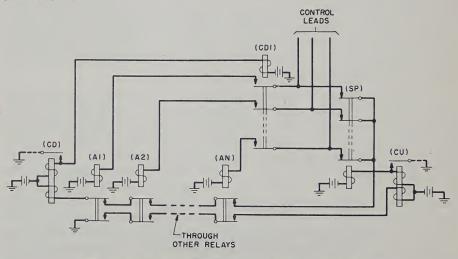

achieve a high degree of balance between the two windings. An example of this is the sandwich winding, where part of one winding is laid on the core, the second winding is next added, and finally the remainder of the first winding is completed. Another example is the parallel type where the wires of the two windings are laid on concurrently. In these cases, the designations  $P_1$  and  $P_2$  are sometimes applied to the two windings instead of P and  $P_2$ .

Other winding arrangements of a much more specialized nature are shown on the remainder of Fig. 2-6. The arrangements shown in Figs. 2-6E, 2-6F, and 2-6G include resistors wound non-inductively on the cores. These serve no purpose that could not be achieved by external resistors, but it may be convenient and economical to include them in the relay structure. The specialized arrangements have little general utility, but may be of use in particular applications.

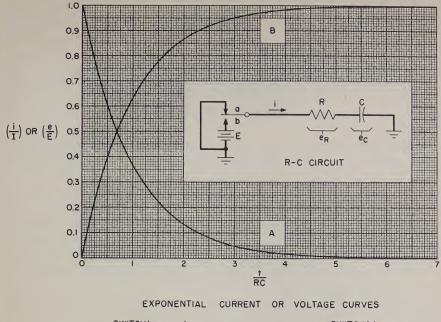

Relay Operating Characteristics and Adjustments. The force which pulls the relay armature to actuate the contact springs is developed by current flowing through the winding. Since the winding is inductive, the initial current does not immediately jump to a value determined by the relay resistance and circuit voltage, but rises exponentially at a rate determined by the time constant of the winding and certain other electric and magnetic properties of the structure. Thus, the contacts do not move until the current has risen to a level where the magnetic flux generated across the armature air gap provides sufficient force to overcome the initial back tension of the armature. When the armature starts to move, the back tension increases as the contact springs are flexed to a greater and greater extent. At the same time, the operating force increases as a function both of the continuing

rise in current and the decreasing reluctance in the magnetic circuit as the air gap closes. The operating force must increase more rapidly than the armature back tension for the relay to operate completely.

For a particular type of relay, the force or pull developed across the armature air gap is a function of the product of the current and the number of turns of the winding. This product is generally known as ampere-turns. It can be seen that, for a specific required pull, there must be a balance among the winding turns, the winding resistance, and the voltage level for which the relay is designed. The resistance and the voltage level are related to the normal power-handling capacity of the relay, which, for general-purpose relays, is usually in the range of one to ten watts.

When the circuit to the relay winding is opened, current flow ceases rather abruptly, unless the winding is shunted, and the relay starts to release. The decay of magnetic flux is affected by eddy currents in the core, by the magnetic material of the relay, by the residual air gap left when the relay is fully operated, and by any conducting paths encircling the core. All these factors, plus the time for mechanical motion, determine the release time of the relay.

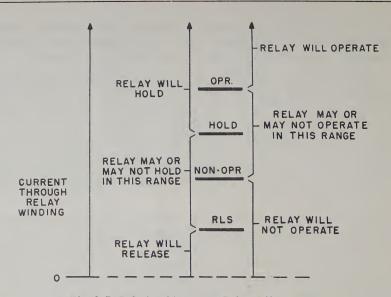

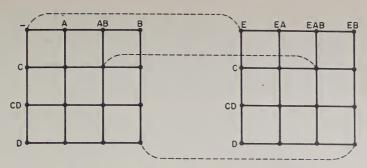

A set of mechanical adjustments is specified for any relay. These have to do with unoperated armature air gap, residual armature air gap (in some cases), direction and limits of spring tension, contact pressure, etc. As determined by the tolerance range of these mechanical adjustments, there are a set of four basic electrical requirements that can be applied to a relay and which determine its operation in a circuit. These are the operate, hold, non-operate, and release requirements, as defined below. The principal mechanical variable which can be changed to make the relay meet the requirements is the spring tension against the relay armature. The requirements are normally specified in terms of current flow.

Operate Requirement: The current level at which the relay will definitely operate. The current at which the relay can operate may extend well below this level.

Hold Requirement: The level to which the current may be reduced, after the relay has operated, which will insure that the relay remains fully operated.

Non-Operate Requirement: The current level at which an unoperated relay definitely will not operate. The relay may operate at any current level above the non-operate value.

Release Requirement: The level to which the current through an operated relay can be reduced with assurance that the relay will completely return to an unoperated condition.

Fig. 2-7 Relationship among Relay Adjustments

Since the same mechanical condition must permit the relay to meet all four electrical requirements, or all that are specified in a particular case, the electrical requirements are necessarily closely interrelated. Setting any one requirement value, such as operate, automatically establishes limits within which the others must fall. If a relay is adjustable, the spring tension is regulated to a compromise value which permits meeting all specified electrical requirements. The status of the relay is then as shown on Fig. 2-7. In practice, however, it is seldom that all four requirements are placed upon a relay. For normal straightforward operation in open and closed circuits, the operate requirement alone may be specified. The others are necessary only to meet marginal conditions, or to hold the relay to special speed requirements.

In order for a relay to function satisfactorily in a circuit, some margin must be left between the circuit current under adverse conditions and the corresponding relay current requirement. Otherwise, a slight change in the mechanical condition caused by temperature or humidity changes or by wear may cause the relay to fail. A margin of 10% is usually considered adequate to take care of this situation. In practice, the worst circuit current is computed under extreme conditions of voltage and resistance limits, and a check made that the resultant value exceeds the operate or hold requirement by 10% or more. For release, the worst circuit current should be less than the

release relay requirement by 10% or more, and should be less than the non-operate requirement by a greater amount if possible.

Operating and Release Times. General-purpose relays are obtainable with acting times ranging from less than five milliseconds up to approximately a half-second. Although acting times above the order of fifty milliseconds require special methods of construction which will be discussed in a later section, the remarks here will apply to relays in general.

For a given mechanical structure, neglecting the effect of any special time-increasing features, the operating time of a relay is a function of several variables. Of these, the most important for present purposes are the spring load on the armature, the unoperated armature air gap, and the power absorbed by the relay winding. For a given winding, the operating time will increase as the spring load on the armature increases and as the unoperated armature air gap increases. The air gap is fixed to a great extent by the spring combination and is not. strictly speaking, an independent variable. For a given spring load, the operating time will decrease as the power to the winding increases. Therefore, the higher the circuit voltage and, assuming the use of welldesigned coils, the lower the coil resistance, the faster will be the relay. These facts are important to the circuit designer since, where speed of operation is important, he must make a careful choice of the winding coil and must not place a large number of contact springs on the relay. The choice of coil is influenced by the circuit voltage, which is generally set by other considerations, and the maximum power that can be applied to the relay without causing excessive heating.

The release time of a relay, again neglecting the effect of any special time-increasing features, is primarily a function of operated spring load and operated armature air gap, the time of release increasing as either of these factors decreases in magnitude. It is worth noting that, to a certain extent, the factors which aid in gaining low operate time tend to increase the release time, and vice versa.

It is difficult to attain a high degree of precision in the operate and release times of general-purpose relays. These times are affected both by the structural variations in the relays and by electrical variations in the circuit. The result of this is that individual relays of a particular type, meeting all mechanical and electrical adjustment limits, may differ in operate or release times by as much as two or three to one. The designer must constantly keep this in mind when attempting to meet delicate circuit time requirements.

An aspect of the time characteristics of relays is the phenomenon of contact stagger. Since a relay does not operate or release instantaneously, there is a finite armature transit time during which contacts

may open or close more or less in a random sequence. Thus, several milliseconds may elapse between the closure of one make contact on a relay and another make contact in the same spring pile-up. The magnitude of the stagger usually increases with the acting time of the relay. Although definite contact sequences can be imposed, either by use of certain spring combinations or by adjustment, it is generally preferable to design the circuit in such a way that it is not affected by random stagger.

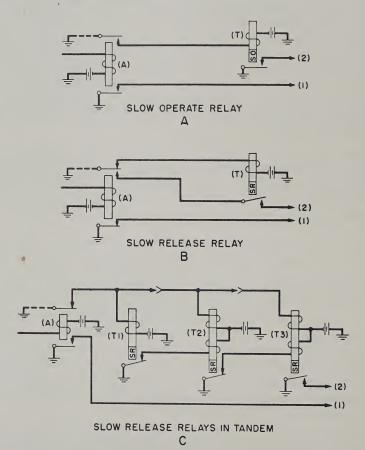

Relay Construction for Slow Action. The acting time of a relay, either on operate or release, can be increased considerably by any means which delays the build-up of magnetic flux (operate) or retards its decay (release). This can be done most simply by encircling the relay core by a conducting path. When the circuit is closed to the winding, induced currents in this path will generate magnetic flux to oppose the operating flux. When the circuit to the winding is opened, induced currents will generate flux in the core in a direction which tends to hold the relay operated. The conducting path has no effect when the steady state of the relay has been reached.

The most frequently used method of achieving these effects is to place a highly conducting sleeve, usually of copper, over the core. The sleeve may extend over the length of the core, or may be concentrated at either end of the structure. With end sleeves, operating time is increased to a much greater extent when the sleeve is located at the front end of the relay, close to the armature air gap, than when the sleeve is displaced toward the rear of the relay. Release time is affected to a much lesser degree by sleeve position.

The effectiveness of sleeves is much greater in increasing the release time than the operate time of a relay. The maximum reliable operate time that can be achieved with a general-purpose relay is well under 0.1 second, while the maximum release time may run as high as 0.5 second or more. It is also true that release time can be more closely controlled than operate time in manufacture. As a result, it is generally preferable to use the release of a relay for delayed action in circuits.

Aside from the use of sleeves, the acting time of relays can be increased to some extent by circuit means. A short-circuited secondary winding, for example, will increase the time of operation and release, particularly the latter. The release of a relay by short-circuiting the operating winding will increase the release time appreciably. Finally, as indicated in the preceding section, the operate time of a relay becomes greater as the circuit current is allowed to approach the operate adjustment value.

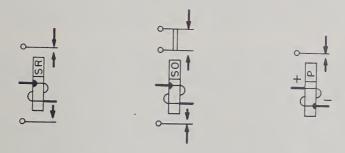

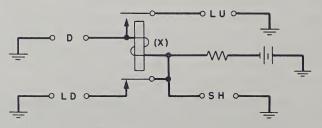

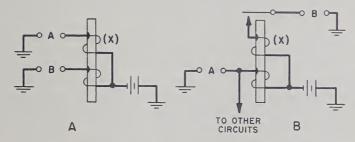

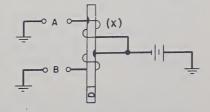

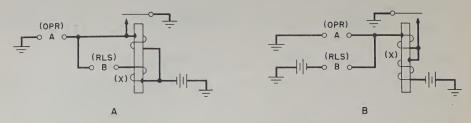

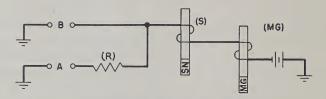

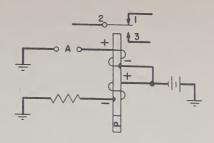

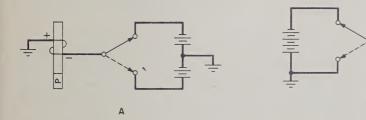

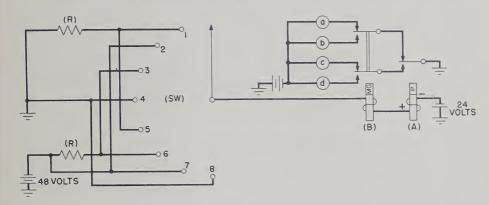

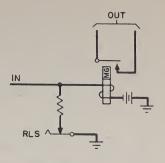

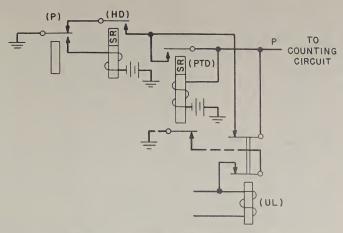

When slow-acting relays, either operate, release, or both, are used in a circuit, it is customary to indicate the nature of the relay on the schematic drawing. This is done by placing code letters such as SR (slow release) in a box, drawn as part of the relay core. Illustrations of this are shown on Fig. 2-8. On the same figure is a list of the more common abbreviations used in similar fashion for indicating other special operating features of relays.

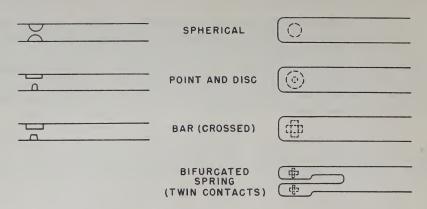

Relay Contacts. The function of a contact on a general-purpose relay is to provide a reliable low-resistance circuit path for its load under specified conditions of current flow, type of load, and total number

AC - alternating current

D - differential

DB - double biased (biased in both directions)

DP - dashpot

EP - electrically polarized

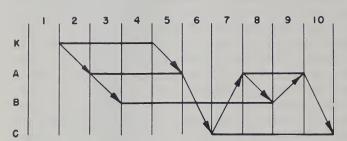

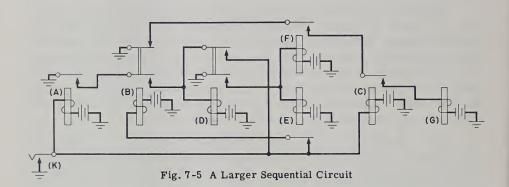

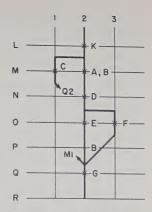

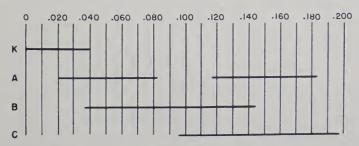

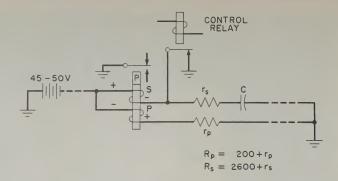

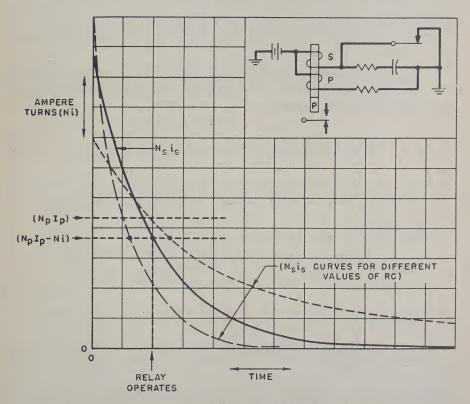

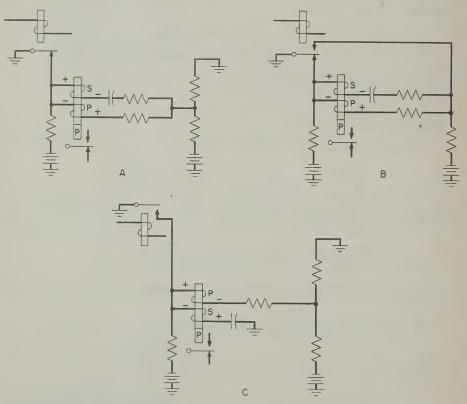

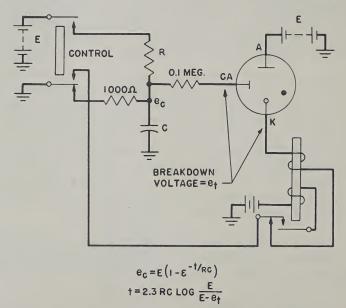

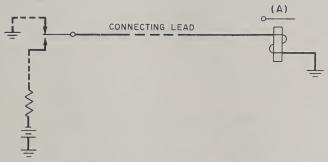

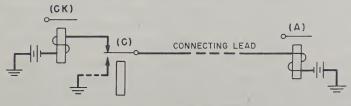

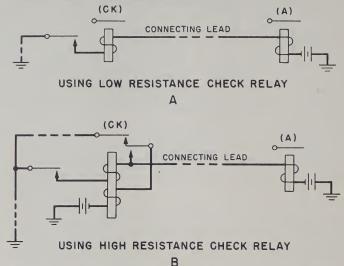

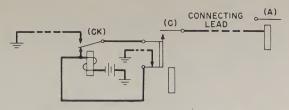

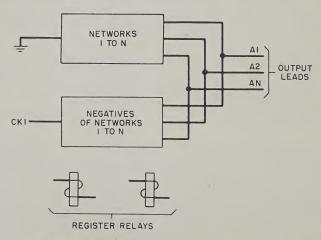

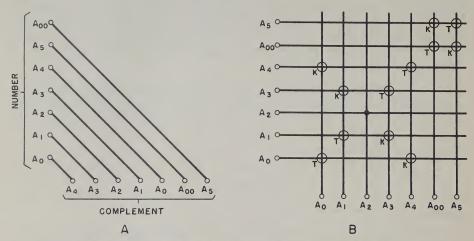

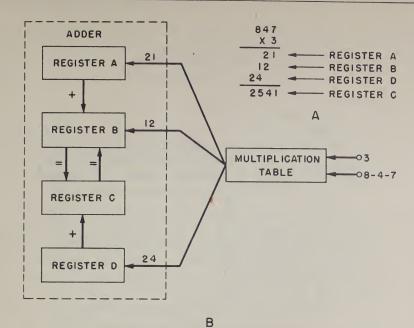

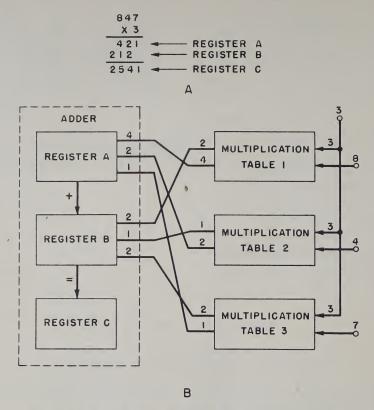

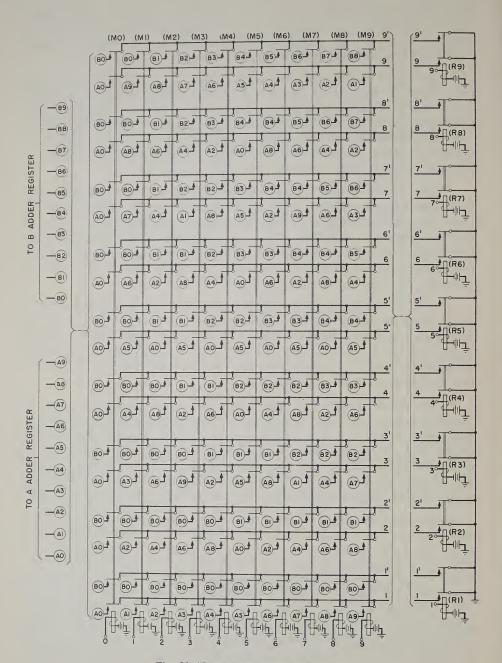

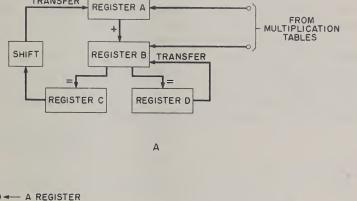

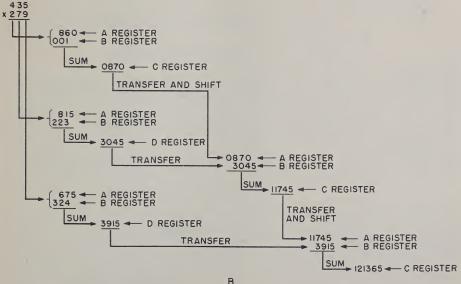

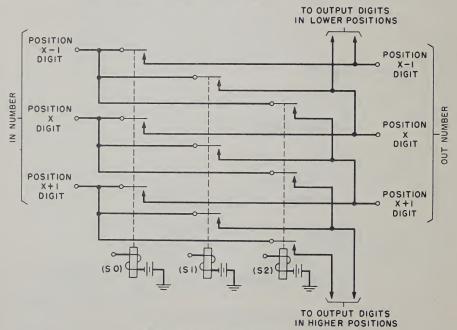

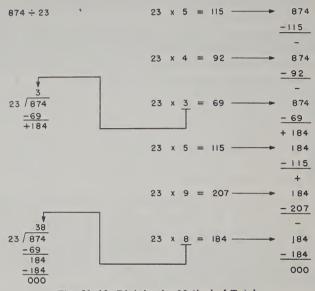

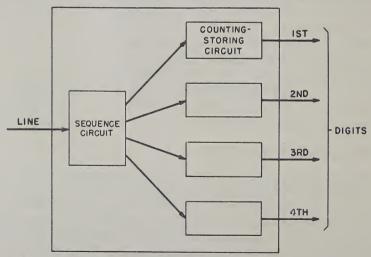

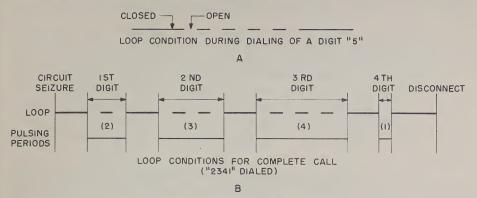

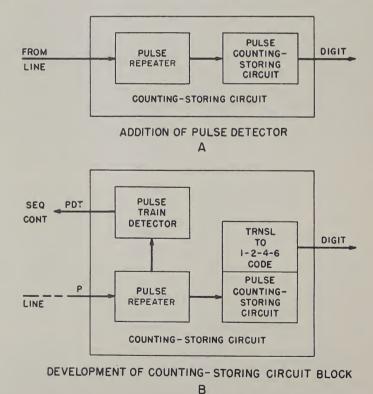

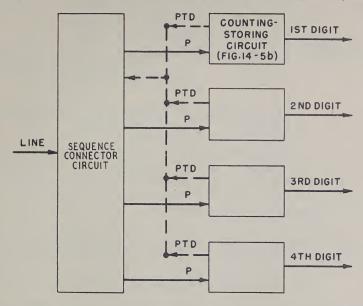

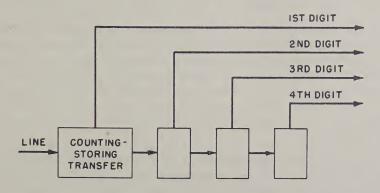

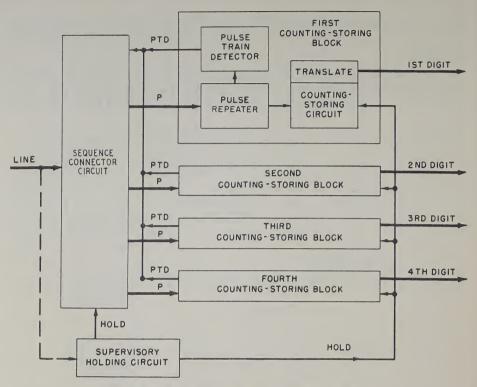

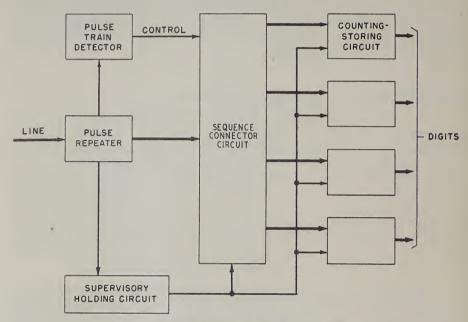

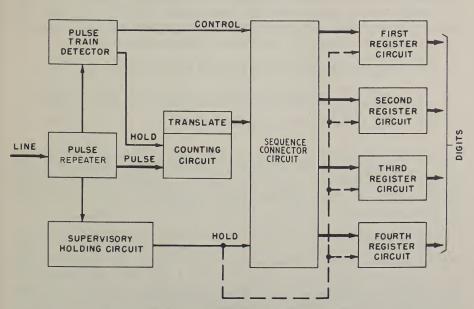

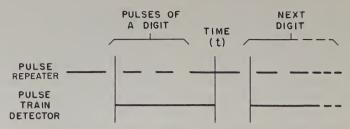

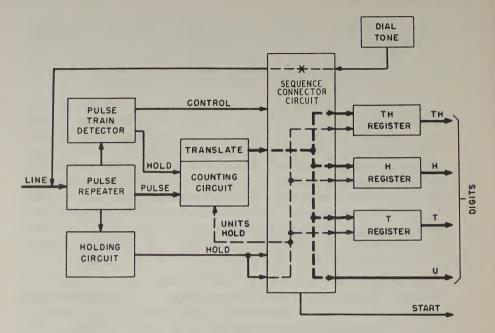

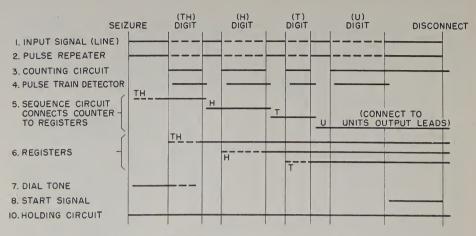

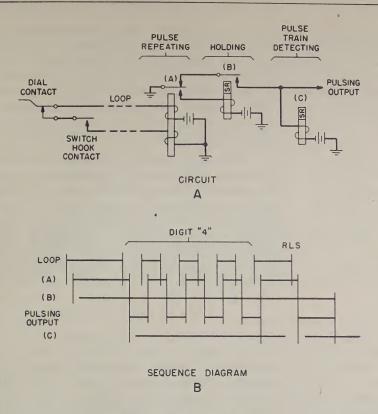

FO - fast operate\*